#### WASHINGTON UNIVERSITY IN ST. LOUIS

McKelvey School of Engineering Department of Computer Science & Engineering

> Dissertation Examination Committee: Roger Chamberlain, Chair Jeremy Buhler Ron Cytron Christopher Gill I-Ting Angelina Lee Xuan Zhang

Efficient Computation Using Near-Memory Processing and High-Level Synthesis by Chenfeng Zhao

> A dissertation presented to the McKelvey School of Engineering of Washington University in partial fulfillment of the requirements for the degree of Doctor of Philosophy

> > August 2024 St. Louis, Missouri

$\bigodot$  2024, Chenfeng Zhao

# **Table of Contents**

| List of | Figures                                             | v               |

|---------|-----------------------------------------------------|-----------------|

| List of | Tables                                              | vii             |

| Ackno   | wledgments                                          | ix              |

| Abstra  | act                                                 | xi              |

| Chapte  | er 1: Introduction                                  | 1               |

| 1.1     | Research Questions                                  | 8               |

| 1.2     | Contributions                                       | 9               |

| 1.3     | Outline                                             | 11              |

| Chapte  | er 2: Background and Related Work                   | 12              |

| 2.1     | Data Integration                                    | 12              |

| 2.2     | Near-Memory Processing                              | 13              |

| 2.3     | Graph Processing                                    | 15              |

| 2.4     | Graph Neural Networks                               | 18              |

| 2.5     | High-Level Synthesis                                | 21              |

| Chapte  | er 3: Executing Data Integration Near the Memory    | 25              |

| 3.1     | Workload Characterization                           | 25              |

| 3.2     | Proposed Near-Memory System                         | 27              |

| 3.3     | Methodology                                         | 29              |

|         | 3.3.1 Near-Memory Processing System                 | 29              |

|         | 3.3.2 Baseline/Host System                          | 30              |

|         | 3.3.3 Wide-Parallel System                          | 30              |

|         | 3.3.4 Simulation                                    | 31              |

| 3.4     | Evaluation                                          | 33              |

| 0.1     | 3.4.1 Performance Improvement                       | 33              |

|         | 3.4.2 Energy Consumption                            | 35              |

| 3.5     | Conclusion                                          | 38              |

| Chapt   | on 4. Pontitioning for Noon Momony Croph Proceeding | 39              |

| -       | er 4: Partitioning for Near-Memory Graph Processing | <b>39</b><br>40 |

| 4.1     |                                                     | 40              |

|        | 4.1.1    | Mixed-Cut Partitioning                                                                                                   |

|--------|----------|--------------------------------------------------------------------------------------------------------------------------|

|        |          | Vertex-Swapping Greedy Algorithm                                                                                         |

|        | 4.1.3    | Partial Graph Repartitioning 43                                                                                          |

|        | 4.1.4    | Three-Phase Programming Model    44                                                                                      |

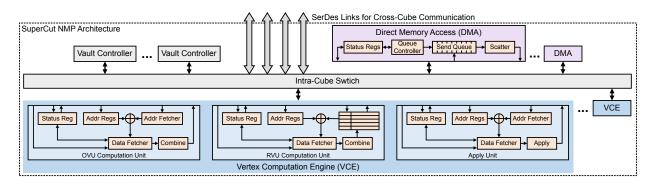

|        | 4.1.5    | Proposed Near-Memory System                                                                                              |

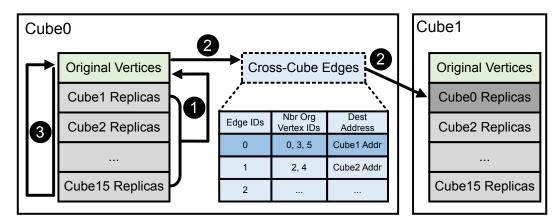

|        | 4.1.6    | Graph Representation                                                                                                     |

| 4.2    | Experin  | nental Methodology                                                                                                       |

| 4.3    | Evaluat  | $tion \dots \dots$ |

|        | 4.3.1    | Energy Consumption and Performance                                                                                       |

|        | 4.3.2    | Mixed-Cut Partitioning                                                                                                   |

|        |          | Memory Footprint                                                                                                         |

|        |          | Simulated Annealing                                                                                                      |

| 4.4    |          | sions $\ldots \ldots 55$      |

| Chapte | er 5: G  | raph Neural Network Inference via High-Level Synthesis 56                                                                |

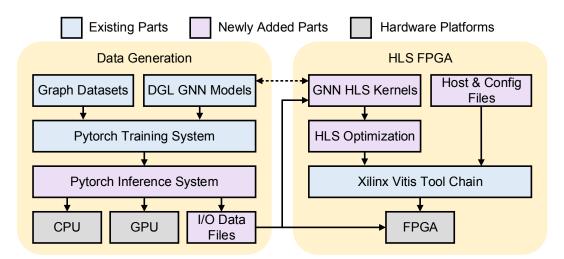

| 5.1    |          | vork Description                                                                                                         |

|        |          | GNNHLS Overview                                                                                                          |

| 5.2    |          | nental Methodology                                                                                                       |

| 5.3    | -        | $terization \qquad \dots \qquad 62$                                                                                      |

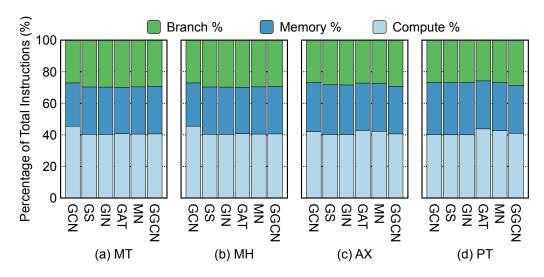

|        |          | Instruction Mix                                                                                                          |

|        |          | Spatial and Temporal Locality                                                                                            |

| 5.4    |          |                                                                                                                          |

|        |          | Resource Utilization 64                                                                                                  |

|        |          | Performance                                                                                                              |

|        |          | Optimization Techniques                                                                                                  |

|        |          | Energy Consumption                                                                                                       |

| 5.5    |          | sions                                                                                                                    |

| Chapte | on G. D. | erformance of HLS-based Graph Neural Networks                                                                            |

| 6.1    | Methoo   | 1                                                                                                                        |

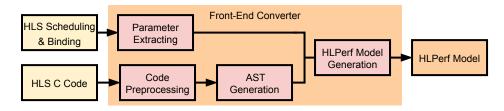

| 0.1    |          | Overall Workflow   73                                                                                                    |

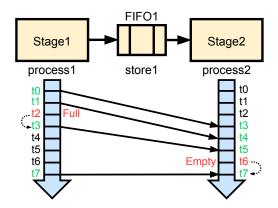

|        |          | Discrete-Event Simulation                                                                                                |

|        |          | HLPerf Model Converter                                                                                                   |

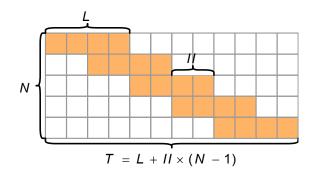

|        |          | Pragma-Driven Pattern Modeling                                                                                           |

| 6.2    |          | per Experience                                                                                                           |

| 6.3    | -        | tion Methodology                                                                                                         |

| 6.4    |          | tion                                                                                                                     |

| 0.4    |          | Simulator Performance                                                                                                    |

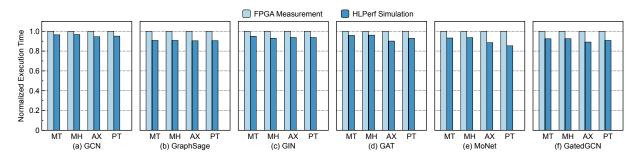

|        |          | Application Performance Prediction Accuracy       91                                                                     |

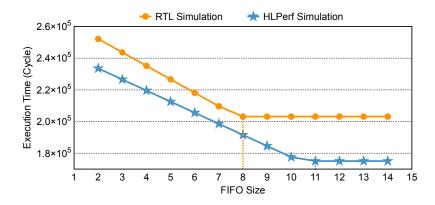

|        |          | FIFO Size Sensitivity                                                                                                    |

|        |          | Identifying Performance Bottlenecks                                                                                      |

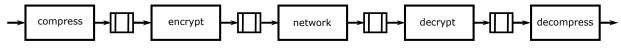

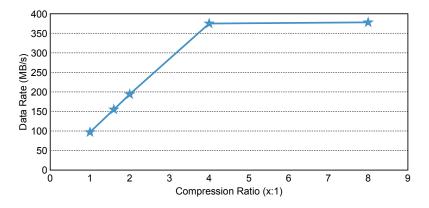

|        |          | General-Purpose Application Evaluation                                                                                   |

| 6.5    |          |                                                                                                                          |

| 0.0    | Conciu   | sions                                                                                                                    |

| Chapter 7: Conclusions and Future Work | 98  |

|----------------------------------------|-----|

| References                             | 101 |

# List of Figures

| Figure 1.1: | Near-memory graph processing system.                                                                    | 4  |

|-------------|---------------------------------------------------------------------------------------------------------|----|

| Figure 2.1: | Interconnection technology of 3D-stacked memory chips                                                   | 14 |

| Figure 2.2: | A single memory cube (left), and topology of the Dragonfly cube-to-cube interconnection network (right) | 14 |

| Figure 2.3: | Conventional HLS workflow (in black) and our contribution (in red). $\ .$ .                             | 21 |

| Figure 3.1: | Workload characterization of data integration workloads                                                 | 26 |

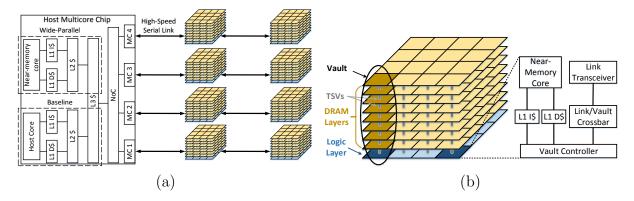

| Figure 3.2: | Architecture of near-memory processing system                                                           | 27 |

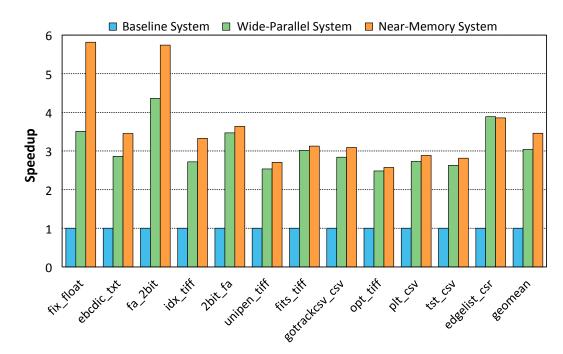

| Figure 3.3: | Speedup of data integration workloads                                                                   | 34 |

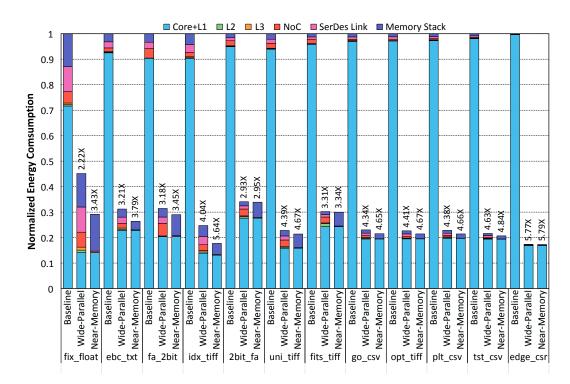

| Figure 3.4: | Energy consumption of data integration workloads                                                        | 35 |

| Figure 4.1: | Example graph for partitioning                                                                          | 40 |

| Figure 4.2: | The partial graph repartitioning method.                                                                | 44 |

| Figure 4.3: | SuperCut near-memory processing architecture                                                            | 46 |

| Figure 4.4: | Diagram of graph representation in Cube0 and data communication. $\ .$ .                                | 48 |

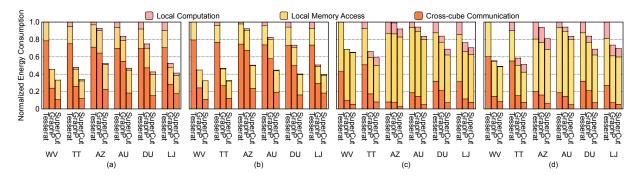

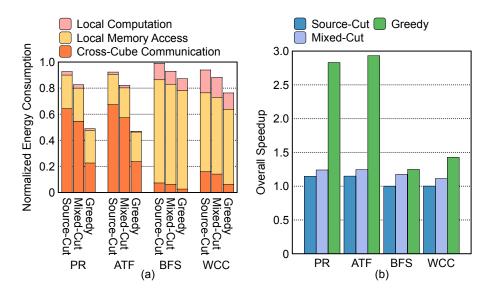

| Figure 4.5: | Normalized energy consumption normalized to Tesseract                                                   | 51 |

| Figure 4.6: | Overall speedup normalized to Tesseract.                                                                | 51 |

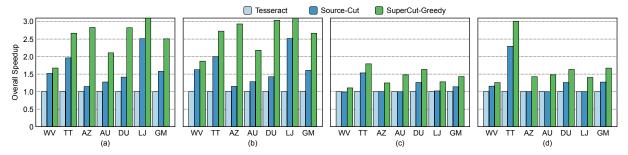

| Figure 4.7: | Average energy delay product and cross-cube communication ratio                                         | 52 |

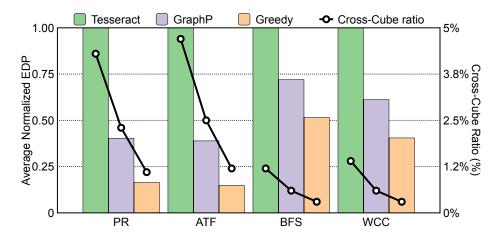

| Figure 4.8: | Energy consumption and overall speedup of mixed-cut partitioning                                        | 53 |

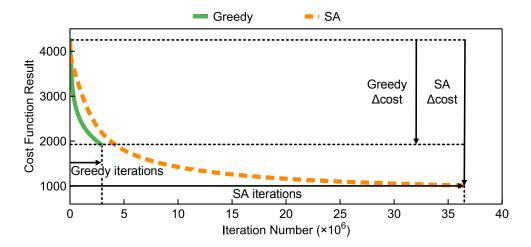

| Figure 4.9: | Simulated annealing and greedy cost function result on Amazon0302                                       | 54 |

| Figure 5.1: | Diagram of the GNNHLS framework.                                                                            | 58 |

|-------------|-------------------------------------------------------------------------------------------------------------|----|

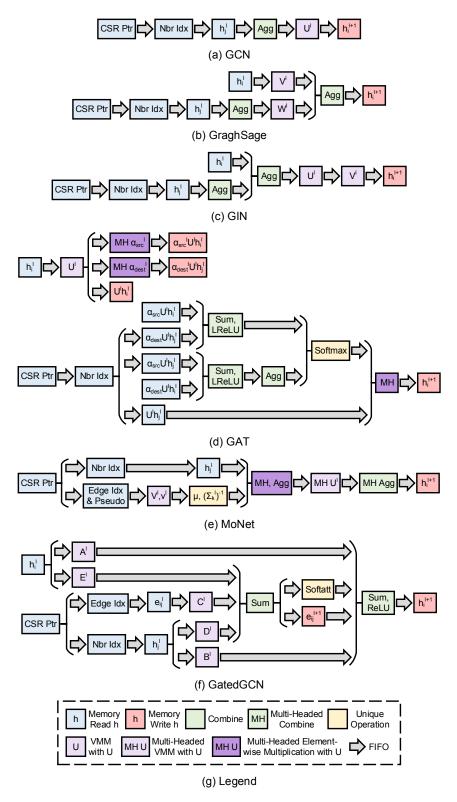

| Figure 5.2: | Dataflow diagrams of GNN HLS kernels in GNNHLS                                                              | 60 |

| Figure 5.3: | Instruction breakdown of all the HLS kernels                                                                | 63 |

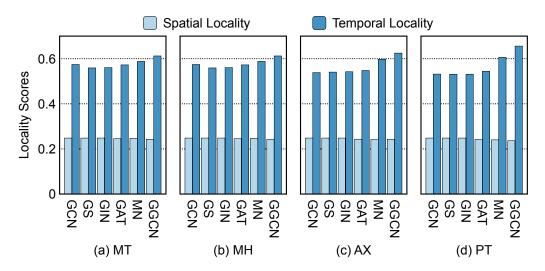

| Figure 5.4: | Memory locality scores of HLS kernels                                                                       | 64 |

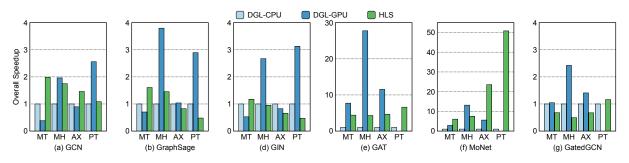

| Figure 5.5: | Speedup of HLS kernels relative to DGL-CPU                                                                  | 65 |

| Figure 5.6: | Energy consumption reduction of HLS kernels.                                                                | 69 |

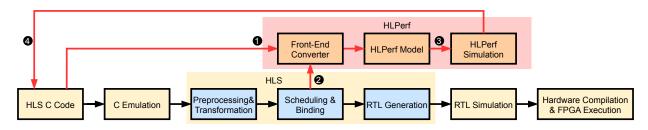

| Figure 6.1: | The overall workflow of HLPerf.                                                                             | 74 |

| Figure 6.2: | An example of SimPy for a dataflow architecture                                                             | 77 |

| Figure 6.3: | The workflow of the Front-End Converter in HLPerf                                                           | 77 |

| Figure 6.4: | Diagram of the latency $(L)$ , initiation interval $(II)$ , and iteration number $(N)$ of a pipelined loop. | 80 |

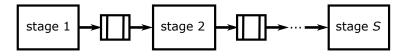

| Figure 6.5: | GNN dataflow pipeline.                                                                                      | 86 |

| Figure 6.6: | Streaming data flow pipeline over a network.                                                                | 86 |

| Figure 6.7: | Normalized HLPerf predicted execution time                                                                  | 92 |

| Figure 6.8: | FIFO size sensitivity                                                                                       | 94 |

| Figure 6.9: | Streaming data pipeline with compression                                                                    | 97 |

# List of Tables

| Table 3.1: | Evaluated system configurations                                                                                                              | 32 |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 3.2: | Energy consumption of data integration workloads                                                                                             | 36 |

| Table 4.1: | Graph dataset.                                                                                                                               | 49 |

| Table 4.2: | Simulated annealing cost results, energy reduction, and speedup. $\ . \ . \ .$                                                               | 55 |

| Table 5.1: | Graph datasets.                                                                                                                              | 62 |

| Table 5.2: | Resource Utilization of HLS GNN models                                                                                                       | 65 |

| Table 5.3: | Execution time on 4 graph datasets                                                                                                           | 65 |

| Table 5.4: | Execution time of various optimization techniques for GraphSage on MH.                                                                       | 68 |

| Table 5.5: | Energy Consumption (J) of DGL-CPU, DGL-GPU, and GNN HLS                                                                                      | 69 |

| Table 6.1: | Graph datasets.                                                                                                                              | 88 |

| Table 6.2: | Simulation elapsed time for HLPerf and RTL simulation, and the speedup of HLPerf relative to RTL simulation.                                 | 89 |

| Table 6.3: | HLPerf simulation elapsed time of all the GNN kernels on 4 graph datasets.                                                                   | 90 |

| Table 6.4: | Elapsed time of conventional HLS workflow procedures, including HLS synthesis steps and hardware compilation.                                | 90 |

| Table 6.5: | Execution time of FPGA measurements (HLS), predicted execution time from HLPerf, and corresponding error rate relative to FPGA measurements. | 92 |

| Table 6.6: | Execution time, error rate, and simulation time of HLPerf for the GCN Kernel with pipelined memory requests.                                 | 95 |

Table 6.7:Execution time, error rate, and simulation time of HLPerf for general-<br/>purpose applications, and the speedup relative to RTL simulation.95

## Acknowledgments

This journey toward earning my PhD is like a phoenix rising from the ashes—challenging yet immensely rewarding. I would like to express my deep appreciation to the many individuals whose support and guidance were essential to my success. Without them, this achievement would not have been possible.

I would like to express my profound gratitude to my advisor, Dr. Roger Chamberlain, whose invaluable support has been instrumental throughout my PhD journey. Dr. Chamberlain is an exceptional mentor, always available to address my queries, no matter how trivial they may seem. His guidance has been crucial in helping me navigate challenges, while his trust and respect have provided me with the freedom to explore the unknown. He has consistently encouraged me when doubts arose about my direction, and has been forthright in correcting my course whenever necessary. With his support, I have not only grasped the essence of research but also sustained my passion for it. Dr. Chamberlain is more than an academic mentor; he is a role model in my life.

I give my sincere gratitude to my co-advisor, Dr. Xuan Zhang, for her invaluable guidance throughout this journey. She consistently offered constructive suggestions on my research projects, from research methodologies to scientific writing. Dr. Zhang's insights and critiques have been crucial in refining my arguments and enhancing the coherence of my findings. Her meticulous attention to detail, passion for discovery, and steadfast dedication to advancing knowledge have profoundly influenced my approach to research. I am deeply grateful for her mentorship and inspired by her commitment to scholarly excellence.

I want to thank my committee members, Dr. Jeremy Buhler, Dr. Ron Cytron, Dr. Christopher Gill, Dr. I-Ting Angelina Lee, for graciously agreeing to serve on my committee. Additionally, I give special thanks to Dr. Jeremy Buhler and Dr. Ron Cytron for their invaluable support and guidance within our research group.

I am deeply grateful for the opportunity to work with a group of exceptionally talented colleagues, including Dr. Anthony Cabrera, Dr. Clayton Faber, Dr. Weidong Cao, Dr. An Zou, Dr. Marion Sudvarg, Dr. Huifeng Zhu, Dr. Justin Deters, Dr. Stephen Timcheck, Dr. Yan Wei,

Dr. Ke Liu, Tianrui Ma, Adith Jagadish Boloor, Steven Harris, Ye Htet, Daisy Wang, and all other members who have since graduated but are not mentioned here. Their encouragement during challenging times has been invaluable. Collaborating with such brilliant individuals has been a truly unforgettable experience.

Finally, I wish to express my deepest gratitude to my parents, Jiang Zhao and Yan Zhang, for their unwavering support and companionship during the most challenging periods of my PhD journey. Our weekly discussions every Friday have been a cornerstone of my perseverance and motivation. The encouragement and comfort they provided have been invaluable, helping me navigate the ups and downs of my academic pursuits. Their belief in my abilities and their constant presence provided the strength I needed to continue, making them an integral part of my success.

This research is supported by NSF under grants CNS-1739643 and CNS-1763503 and a gift from BECS Technology, Inc. We are grateful for the use of the Open Cloud Testbed [52, 120] as an experimentation platform.

Chenfeng Zhao

Washington University in St. Louis August 2024

#### ABSTRACT OF THE DISSERTATION

#### Efficient Computation Using Near-Memory Processing and High-Level Synthesis

by

Chenfeng Zhao Doctor of Philosophy in Computer Engineering Washington University in St. Louis, 2024 Professor Roger Chamberlain, Chair

With the diminishing of Moore's law and the end of Dennard scaling, alongside the explosion of data, the need for efficient computation—both in terms of performance and energy consumption—has become paramount. This is particularly crucial for processing large-scale data across various workloads. While a universal computation method is highly desirable, the inherent unique characteristics of different applications and datasets preclude a one-sizefits-all solution. It is usually the case that an appropriate computation technology choice could benefit a particular set of workloads and vice versa. Addressing this challenge requires designers to possess profound knowledge and insights into both hardware and software. Thus, the field of efficient computation involves many research questions driven by applications and platforms.

In this dissertation, we focus on three representative types of applications: data integration, irregular graph processing, and graph neural networks. Our work in efficient computing leverages Near-Memory Processing (NMP) with 3D-stacked memory and High-Level Synthesis (HLS) on Field-Programmable Gate Arrays (FPGAs) to accelerate these workloads. We start the dissertation by adopting NMP technology based on 3D-stacked memory to accelerate data integration applications in terms of performance and energy consumption. We then present SuperCut, a novel hardware/software graph partitioning framework for near-memory graph processing. Subsequently, we describe GNNHLS, an open-source framework for the

comprehensive evaluation of Graph Neural Network (GNN) kernels on FPGAs using high-level synthesis. Given the complexities of optimizing GNN HLS, we introduce HLPerf, an opensource, simulation-based performance evaluation framework for dataflow architectures that both supports early exploration of the design space and shortens the performance evaluation cycle.

### Chapter 1

### Introduction

In this era of data explosion, the 3Vs of Big Data (volume, velocity and variety) defy the traditional mechanisms of data collection, management and processing. In traditional mechanisms, a large volume of data generated from a variety of fields, such as machine learning, astronomy and bioinformatics, is collected from memory to processors, processed by CPUs, and then written back to memory. Large-volume data transfer between host-side processors and memory becomes a bottleneck of the system due to the memory wall [100]. Memory technology has not been able to keep pace with the development of CPUs in traditional architecture in terms of performance (either latency or bandwidth) and energy consumption. In order to bridge this gap, multiple levels of cache with higher speed and lower capacity are added between processors and main memory, so that data is moved to caches from the main memory first and then processed by computation cores. In practice, many data-intensive applications with sufficient cache locality/utilization benefit from this multi-level memory hierarchy because a number of expensive memory accesses are avoided and replaced with less expensive cache accesses to process reused data. However, for some other data-intensive applications, the conventional CPU-centric system with multi-level memory hierarchy is not able to improve or even exacerbates the performance and energy consumption during execution. There are several challenges in these systems:

- Narrow memory channels consisting of limited number of pins on the memory package cannot provide sufficient bandwidth to meet the ever-growing demands of modern multi-processor designs.

- Long data path as well as cache miss overhead caused by applications with low data reuse running on a multi-level memory hierarchy results in high latency.

- Energy consumption of data movement between host processors and memory becomes a key contributor to the total energy consumption of the system for data-intensive

applications. For example, 66.7% of total system energy on average when implementing Google workloads on customer devices is spent on the host-memory data movement [12].

To solve the challenges above, the concept of near-memory processing (NMP), also called processing-in-memory (PIM), has been proposed. The idea of NMP is to implement computation closer to where data resides. To realize this idea, light-weight NMP cores are integrated into the memory chip. By offloading specific computation targets to these cores near the memory and running them in parallel, the expensive cost of host-memory data movement can potentially be eliminated.

The emergence of 3-D stacked memory technology has opened the door for practical deployment of processor cores near the physical DRAM. The structure of these memories has multiple DRAM chips stacked on top of a single logic chip. These chip layers are connected by vertical high-bandwidth and low-power through-silicon vias (TSVs). The logic layer at the bottom consists of both interconnections and controller logic. In current commercial implementations, the logic layer is not fully utilized (i.e., there is a portion of unused area on the chip). Therefore, the research community has considered integrating general-purpose processor cores or custom accelerators into the logic layer as an approach to implementing a near-memory processing strategy.

Given the variety of characteristics of different applications, the utility of Near-Memory Processing (NMP) technology, particularly when applied to workloads involving 3D-stacked memory cubes, remains uncertain in terms of performance enhancement and energy efficiency for specific applications. This dissertation investigates the application of NMP technology to accelerate two representative types of applications: 1) data integration applications characterized by regular patterns, and 2) conventional graph processing workloads, which typically exhibit irregular patterns.

Data Integration is a term frequently used for the general problem of taking data in some initial form and transforming it into a desired form. While the individual transforms are each (mostly) quite straightforward, the task is quickly complicated by the fact that individual data streams can be quite large and there are frequently many streams, each requiring a distinct transformation specification. Tens to hundreds of multi-gigabyte data streams must be concurrently integrated, and this must be done prior to the real data analysis, the ultimate goal. The issue of how to effectively achieve data integration is a pain point for enterprise data, sensor data, scientific data, financial data, to name a few.

Here, we investigate the use of near-memory processing to execute data integration tasks. In particular, we seek to exploit two properties that are common to many data integration workloads and are well-suited to execution on near-memory processing architectures.

- 1. Abundant parallelism data integration workloads are, for the most part, embarrassingly parallel, so their performance scales well with large numbers of processor cores. Relative to traditional computing systems, the majority of near-memory processing architectures employ a larger number of smaller cores.

- 2. Substantial data movement they are also characterized by having a large fraction of their operations data movement instructions, implying a strong sensitivity to the architecture of the memory subsystem. A central feature of near-memory processing systems is the proximity of the processor cores to the memory.

We explore the impact of each of these properties, quantifying both the performance implications and energy savings achievable though the use of near-memory processing architectures for executing data integration workloads. Overall, for the particular near-memory processing system modeled, the performance improved an average  $3.5 \times$  and the energy reduced an average  $4.2 \times (76\%)$  relative to a traditional baseline system.

Our second application class of interest is graph processing. Due to their ability to capture the complex dependencies and relationships among individual data elements, graphs constitute an important data structure that have been widely used to represent social networks, citation networks, road networks, genome sequences, etc. The recent proliferation of graph processing applications, including machine learning [99], recommendation systems [67], and social network analysis [77], has heightened the need for efficiently processing graphs, both in terms of performance and energy consumption. Hence, a number of approaches have been proposed to efficiently process large-scale graphs [36, 61, 64, 70, 118].

The inherent properties of graph analytic applications pose challenges for conventional memory and communications systems, which in turn become performance bottlenecks. First, the operation of traversing neighbourhood vertices shows poor locality due to random memory accesses. Second, many graph algorithms have high memory bandwidth requirements because the node-level computation is relatively simple. Third, when executing in parallel, frequent data movement across the system puts pressure on the communications network.

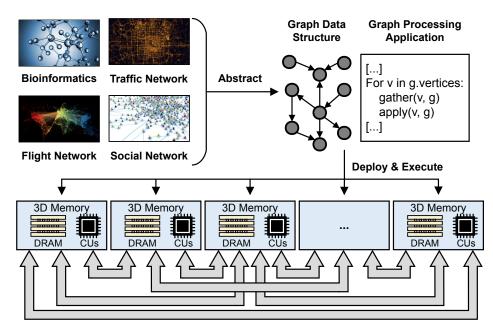

Since the demand for higher memory bandwidth is an important part of accelerating largescale graph processing, Near-Memory Processing has been proposed to accelerate these tasks. Figure 1.1 illustrates a general abstraction of near-memory graph processing systems. Realworld information is abstracted into graph data structures. Graph processing applications are deployed to computing units inside memory chips and executed in parallel. Interaction between memory chips is communicated via an interconnection network.

Figure 1.1: Near-memory graph processing system.

Executing graph processing applications on NMP architectures is distinct from traditional systems for a pair of reasons. First, the number of compute nodes can scale up substantially in a shared-memory paradigm since cache coherence is often not needed. Second, delivering information between compute nodes utilizes mechanisms that are substantially less heavy-weight than traditional message-passing protocols.

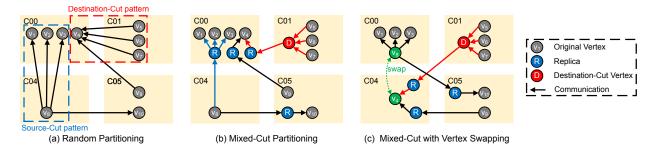

Subsequent works have proposed to diminish communication bottlenecks by alternative preprocessing of the graph [108] or by run-time adaptations [7,8]. GraphP [108] proposes *source-cut* partitioning, in which replicas of the source vertex of each cross-cube edge are deployed in destination cubes, so that multiple cross-cube edges sent from a common source

vertex to the same destination cube can be reduced to one. Therefore, lower cross-cube communication volume is required relative to Tesseract.

Despite the promising results from source-cut partitioning, there is still room for improvement. We observe that after performing source-cut partitioning, cross-cube communication still takes a significant portion of execution time (12%-78%) and energy consumption (14%-73%). This invites the open research question: how effectively can partitioning algorithms reduce communications overheads while maintaining computational balance in an NMP system? To further explore this question, we introduce a hardware/software co-design framework for near-memory graph processing, called SuperCut, and evaluate its effectiveness. To evaluate our framework, we build a multi-cube, near-memory processing simulation platform with reconfigurable logic kernels as computing units by extending gem5-SALAM [76]. Our evaluation results show that SuperCut provides up to  $1.8 \times$  total energy reduction and  $2.6 \times$  speedup with 45% lower extra memory footprint relative to GraphP.

Besides traditional graph processing applications, machine learning (ML) on graphs has experienced a surge of popularity in the past decade, since traditional ML models, which are designed to process Euclidean data with regular structures, are ineffective at performing prediction tasks on graphs. Due to their simplicity and superior representation learning ability, graph neural networks (GNNs) [29, 49, 90, 103, 107] have achieved impressive performance on various graph learning tasks, such as node classification, graph classification, etc.

To implement GNNs, a set of widespread libraries, such as PyTorch Geometric (PYG) [34] and Deep Graph Library (DGL) [93], are built upon general-purpose ML frameworks (e.g. PyTorch [71]) targeting CPU and GPU platforms. However, the performance and energy consumption of GNN implementations are hindered by both hardware platforms and software frameworks:

- 1. Distinct from traditional NNs and graph processing workloads, GNNs combine the irregular communication-intensive patterns of graph processing and the regular computationintensive patterns of NNs. This feature can lead to ineffectual computation on CPUs and GPUs.

- 2. Since these frameworks assemble functions in a sequential way, one function will not start until the previous one finishes. This execution model leads to extra memory

accesses, footprint, and implicit barriers for intermediate results, limiting the potential performance, energy consumption and the scale of graph datasets.

Field-Programmable Gate Arrays (FPGAs) are potentially an attractive approach to GNN inference acceleration. FPGAs' massive fined-grained parallelism provides opportunities to exploit GNNs' inherent parallelism. They also deliver better performance per watt than general-purpose computing platforms. In addition, FPGAs' reconfigurability and concurrency provide great flexibility to solve the challenges of hybrid computing patterns and ineffectual execution. Most of the prior works investigating FPGAs focus on accelerating a specific GNN model implemented using hardware description languages (HDL). AWB-GCN [35], as one of the earliest FPGA-based works, proposes a GCN accelerator using HDL to solve the workload imbalance problem due to the distinct sparsity of different components. BoostGCN [106] proposes a graph partition algorithm in a preprocessing step to address workload imbalance issues. Despite these promising results, HDL design methodology is not suitable for widespread adoption for GNN implementations due to the conflict between the non-trivial development efforts with HDL and the rapid emergence of new GNN models. To address this challenge, high-level synthesis (HLS) tools are proposed to create GNN kernels using popular languages such as C/C++. With the help of HLS, development time is substantially shortened relative to HDL designs. Lin et al. [60], as one of the first works, proposes an HLS-based accelerator for GCN with separated sparse-dense matrix multiplication units and dense matrix multiplication units which are connected by shared memory and execute sequentially. GenGNN [2] proposes a framework to accelerate GNNs for real-time requirements where the whole graph and corresponding intermediate results are stored in on-chip resources on the FPGA. Despite these promising results, this work is limited to small-scale graphs with low edge-to-node ratio due to on-chip memory usage being proportional to graph scale and feature dimensions.

Distinct from pure software programming, HLS developers need to adopt multiple optimization pragmas and follow certain coding styles to achieve best performance and energy cost. As reported in [15], the performance difference between a well-optimized version and a non-optimized version of the same kernel can be two to three orders of magnitude. This invites an open question: how effectively can modern HLS tools accelerate GNN inference?

We introduce GNNHLS an open-source framework for comprehensive evaluation of GNN kernels on FPGAs via HLS. GNNHLS contains a software stack extended from a prior GNN benchmark [31] based on PyTorch and DGL for input data generation and conventional

platform baseline deployments (i.e., CPUs and GPUs). It also contains six well-optimized general-purpose GNN applications. These kernels can be classified into 2 classes: (1) isotropic GNNs in which every neighbor contributes equally to the update of the target vertex, and (2) anisotropic GNNs in which edges and neighbors contribute differently to the update due to the adoption of operations such as attention and gating mechanisms. Our evaluation results show that GNNHLS provides up to  $50.8 \times$  speedup and  $423 \times$  energy reduction relative to the multicore CPU baseline. Compared with the GPU baselines, GNNHLS achieves up to  $5.16 \times$  speedup and  $74.5 \times$  energy reduction.

Although HLS bridges the gap between software and hardware development, optimizing HLS codes is substantially distinct from conventional software programming. In fact, due to the FPGAs' inherent attributes, such as lack of built-in cache mechanisms, low clock frequency (relative to traditional processor cores), and fine-grained configurability, the performance difference between a well-optimized version and naive version of the same kernel can be two or three orders of magnitude [15, 32, 85]. Therefore, to achieve the best performance, HLS developers need to explore a large optimization space for HLS designs with various optimization pragmas, coding paradigms, etc.

As the complexity of kernels increases, optimizing (or auto-optimizing) such kernels is difficult via conventional HLS workflows for several reasons:

- 1. Since pure C emulation is only designed for functionality verification, current HLS developers have to use RTL simulation to understand performance by manually mapping the results of individual signals in the generated waveform back to the HLS code. However, since all the signal names are auto-generated, they are not easily comprehensible by users. Besides, RTL simulation usually takes a very long time, making the tuning effort arduous. Even worse, it is exacerbated by the fact that tuning with a small example data set is less meaningful for GNN kernels in terms of performance estimation because of the inherent irregularity of graph datasets and algorithms. In other words, distinct graph topologies can significantly impact the final performance achieved. Therefore, when it comes to large-scale graphs, RTL simulation is impractical to be used to optimize GNN kernels with these graphs.

- 2. The notion of dataflow architectures which exploit task-level parallelism, where multiple functions are connected by FIFOs and executed concurrently instead of sequentially, further mystifies the optimization process because it induces a wider set of design

space challenges including: task partitioning, FIFO depth tuning, and bottleneck identification, which are distinct from conventional computation platforms.

The critical missing piece in the optimization task is the availability of fast, high-quality understanding of the performance implications of the design choices that are made. In this work we seek to address this missing element, providing the the designer (whether it be a human or an automatic design space exploration tool [80]) with performance predictions both quickly and with sufficient accuracy that they can be used effectively.

Traditional approaches to performance assessment either involve static assessment (i.e., compile-time analysis) or cycle-accurate simulation. In this work, we propose a different method, effectively between the approaches of static estimation and cycle-accurate simulation, to investigate the impact of irregularity of data and algorithms on performance. Due to the existence of other HLS tools for functional verification (e.g., software emulation in Vitis), our method decouples functional verification from performance estimation, so that the runtime of the estimation process is independent of the computational details of the FPGA algorithms.

We introduce HLPerf, a performance evaluation methodology that supports the performance variations inherent in data-dependent algorithms (it is simulation based), but relaxes the notion of cycle accuracy and replaces it with "approximate" cycle accuracy. The result is a simulation-based performance estimate that is two orders-of-magnitude faster than state-of-the-art simulations that perform cycle-accurate functional verification.

#### **1.1** Research Questions

In this dissertation, we seek to address the following questions:

- To what extent does NMP benefit data integration applications?

- To what extent can NMP benefit graph processing applications?

- How effectively can modern HLS tools accelerate GNN inference in terms of performance and energy consumption?

• How can we provide the developer of GNN HLS designs with fast performance prediction and sufficient accuracy?

### **1.2** Contributions

In this dissertation, we make the following specific contributions:

- 1. Contributions to data integration applications.

- Characterize data integration workloads to gain insights on the suitability and potential performance benefits of executing data integration near the memory [115].

- Quantitatively evaluate near-memory processing for the execution of data integration workloads [115].

- Assess both the performance improvement and energy savings that are achievable, and separately examine the distinct implications of wider parallelism (i.e., a larger number of simpler cores) and lower memory access overheads (i.e., physical location of the cores near the memory) [115].

- 2. Contributions to graph processing applications.

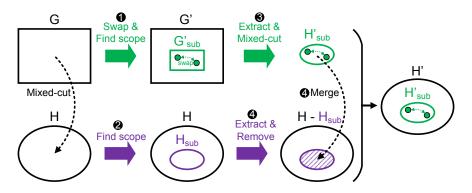

- Propose a set of graph partitioning algorithms, containing: (1) a *mixed-cut* partitioning method which reduces communication volume by recognizing more cross-cube edge patterns, and (2) a *vertex-swapping-based greedy* algorithm to further reduce communication volume by iteratively changing the vertex distribution [110, 111].

- Propose a *three-phase programming model* that is expressive for general vertex programs and explicitly handles computation and communication via user-defined functions along with a custom graph representation to bridge the software and hardware design while diminishing the irregularity of vertex traversal and communication [110, 111].

- Generate specialized accelerators via high-level synthesis (HLS) and map them to FPGA resources on the logic layer of 3D-stacked memory cubes [110, 111].

- 3. Contributions to graph neural networks.

- Propose GNNHLS<sup>1</sup>, a framework to evaluate GNN inference acceleration via HLS, containing: (a) a software stack based on PyTorch and DGL for data generation and baseline deployment, and (b) FPGA implementation including 6 well-tuned GNN HLS kernels with host and configuration files which can also be used as benchmarks [112].

- Characterize the GNN kernels in terms of locality scores and instruction mix to obtain insight into their memory access and computational properties [112].

- Provide a comprehensive evaluation of our GNN HLS implementations on 4 graph datasets, assessing both performance improvement and energy reduction [112].

- Propose HLPerf, an open-source<sup>2</sup>, approximately-cycle-accurate performance evaluation method, to estimate the dynamic performance of GNN HLS kernels with a dataflow architecture. It gives useful performance guidance with dramatically better simulation speed than both RTL simulation and more recently developed cycle-accurate simulators [112].

- Describe an approach to automatically transform the HLS C-based source code describing several GNN operations into simulation components [114].

- Propose a set of high-level quantitative expressions in HLPerf to model the performance impact of various optimization techniques. Decoupling performance estimation from functional verification, HLPerf is faster and can be used to guide dataflow pipeline designs even prior to the authoring of the constituent HLS kernels [114].

- Provide a comprehensive evaluation of HLPerf using 6 different GNN models on 4 graph datasets plus several additional general-purpose applications, assessing both accuracy of the performance predictions and performance of the simulator itself. Our evaluation results show that the error rate of HLPerf is 7% on average and it is 13500× faster than RTL simulation and over 400× faster than a state-of-the-art cycle-accurate simulator [114].

<sup>&</sup>lt;sup>1</sup>Released as a benchmark suite [113] and also available at https://github.com/ChenfengZhao/GNNHLS <sup>2</sup>Available at https://github.com/ChenfengZhao/HLPerf

### 1.3 Outline

The dissertation is organized as follows. Chapter 2 gives related work and background information on data integration, near-memory processing, graph processing, GNNs, and HLS. Chapter 3 describes the work in which we adopt near-memory processing to both accelerate the execution of data integration workloads and reduce their energy needs. Chapter 4 introduces SuperCut, a graph partitioning framework for near-memory architectures to effectively reduce communication overheads while maintaining computational balance. Chapter 5 presents GNNHLS, a framework to evaluate GNN inference acceleration via HLS. Chapter 6 provides HLPerf, an open-source, simulation-based performance evaluation framework for dataflow architectures that both supports early exploration of the design space and shortens the performance evaluation cycle. Chapter 7 gives conclusions and future work.

### Chapter 2

### **Background and Related Work**

#### 2.1 Data Integration

Data Integration is a term frequently used for the general problem of taking data in some initial form and transforming it into a desired form. While the individual transforms are each (mostly) quite straightforward, the task is quickly complicated by the fact that individual data streams can be quite large and there are frequently many streams, each requiring a distinct transformation specification. Tens to hundreds of multi-gigabyte data streams must be concurrently integrated, and this must be done prior to the real data analysis, the ultimate goal.

In graph analysis, for example, Malicevic et al. [65] describe an improvement to a breadth first search algorithm that results in a  $3\times$  improvement in execution time for the breadth first search in isolation. However, it requires the graph data to be in a different form, and when one includes the necessary pre-processing in the performance measurement, the overall execution increases by  $1.5\times$ . In cloud micro-services, Pourhabibi et al. [73] report that up to 30% of execution time is currently spent in the data format transforming process, and as protocol processing is improved by the use of smart NICs that fraction will only increase. The issue of how to effectively achieve data integration is a pain point for enterprise data, sensor data, scientific data, financial data, etc.

In this dissertation, we explore the degree to which near-memory processing techniques (the technology for which is described next) can benefit data integration applications.

### 2.2 Near-Memory Processing

Early NMP systems were based on traditional 2D memory chip and proposed in the 1990s. One of the early proposals is called IRAM [51], the key idea of which is putting a vector processor inside a 2D embedded DRAM chip so that multimedia applications could exploit data parallelism with benefits such as high bandwidth, low latency and low energy consumption. In spite of the promising results, the adoption of these 2D-memory-based NMP architectures was limited by the difference in process technology between computation cores and memory logic.

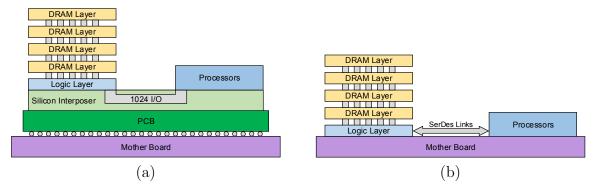

The emergence of 3-D stacked memory technology has provided a practical opportunity for realizing this vision [83]. These 3-D memories consist of multiple DRAM chips stacked on top of a single logic chip. The chips are connected by multiple vertical through-silicon vias (TSVs). The logic layer at the bottom consists of both interconnection and controller logic. The controller logic serves as memory controller to access DRAM and interconnection logic is designed to manage the data transfer between the stacked memory and the processor chip. In this way, the DRAM layers can be accessed with higher bandwidth and lower power than conventional off-chip memory channels. The underutilized logic layer has both area and power available for integrating compute functions [74, 115]. Commercial offerings include the early Hybrid Memory Cube (HMC) [43] as well as High Bandwidth Memory (HBM) [44]. Figure 2.1 shows the interconnection techniques used by HBM and HMC. Illustrated in Figure 2.1(a), HBM utilizes 2.5D system-in-package (SiP) memory technology, in which a silicon interposer offering an I/O density of 1024 bits connects the memory stack with the underlying circuit board and the logic processor. In contrast, HMC adopts four on-board SerDes links as interconnection to provide high bandwidth, shown in Figure 2.1(b). While there are variations across the specific implementations, the core technology is common. To facilitate fair comparison with earlier work, we use technology parameters from HMC in our simulation models.

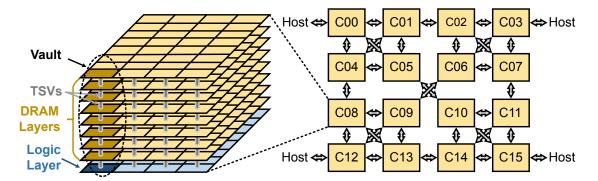

Figure 2.2 (on the left) shows the structure of a single memory cube. Each cube is divided into 32 vertical partitions called vaults and has 4 SerDes high-speed links to implement off-chip accesses. With each cube having a capacity of 8 GB, each vault has a capacity of 256 MB. The logic layer at the bottom of the stack consists of both interconnections and vault controller logic. Each vault can provide 10 GB/s bandwidth. Therefore, the internal bandwidth of each cube is 320 GB/s. For off-chip access implemented by the SerDes links,

Figure 2.1: Overview of interconnection technology of 3D-stacked memory chips. (a) 2.5D system in package (SiP) technology adopted by HBM and (b) SerDes links adopted by HMC.

each link can provide a bandwidth of 120 GB/s. Each cube then has an external bandwidth of 480 GB/s. In addition, each cube has unused area on its logic layer. Previous works [3,12] report that the spare area is about 60 mm<sup>2</sup>, comprising 26.5% of the the total die area (226 mm<sup>2</sup> per cube [82]). Since the logic layer is not fully utilized in current commercial implementations (i.e., there is a portion of unused area on the chip), the research community has considered integrating general-purpose processor cores or custom accelerators into the logic layer as an approach to implementing a near-memory processing strategy.

Figure 2.2: A single memory cube (left), and topology of the Dragonfly cube-to-cube interconnection network (right).

Due to the flexibility of the SerDes links, various interconnect topologies can be considered. One prevalent topology is Dragonfly [48], which has high connectivity and a low network diameter. Figure 2.2 (on the right) shows a Dragonfly interconnection network with 16 cubes. Unused links are used to provide connectivity to host cores. We use the Dragonfly network topology in this work. For the 16 cube system, the aggregated internal memory bandwidth is 5 TB/s while the bisection bandwidth of the interconnection network is only 480 GB/s, implying that inter-cube communications can easily become a performance limiter [24, 108]. In addition to performance, prior work [7] reports that cross-cube communication is also the primary source of energy consumption in graph processing applications, taking up 62% of the total.

There have been a number of proposed near-memory processing (NMP) architectures. Drumond et al. [30] proposed an architecture that utilizes general-purpose Arm Cortex-A35 CPUs as near-memory processing cores. In addition, they altered the execution of common data analytic operators to be more NMP-friendly by optimizing for sequential memory accesses over random memory accesses. Boroumand et al. [12] proposed a near-memory processing architecture with either general-purpose cores or programmable accelerators for Google workloads. Peng et al. [72] explored the suitability of HPC scientific applications on an NMP architecture with general-purpose cores as the execution unit. Our work also utilizes general-purpose programmable cores with small caches in the NMP architecture. However, compared to these prior works, we focus on a different application domain. There has also been recent work utilizing custom logic as execution units. For example, Jang et al. [42] present a accelerator-based NMP architecture for a set of primitives in garbage collection workloads. Singh et al. [83] recently published a survey of the field. In this dissertation, we seek to exploit these ideas for acceleration of data integration workloads.

### 2.3 Graph Processing

The recent proliferation of graph processing applications, including machine learning [99], recommendation systems [67], and social network analysis [77], has heightened the need for efficiently processing graphs, both in terms of performance and energy consumption. Hence, a number of approaches have been proposed to efficiently process large-scale graphs [36,61,64,70, 118]. The inherent properties of graph analytic applications pose challenges for conventional memory and communications systems, which in turn become performance bottlenecks. First, the operation of traversing neighbourhood vertices shows poor locality due to random memory accesses. Second, many graph algorithms have high memory bandwidth requirements because the node-level computation is relatively simple. Third, when executing in parallel, frequent data movement across the system puts pressure on the communications network. Since the demand for higher memory bandwidth is an important part of accelerating large-scale

graph processing, Near-Memory Processing (NMP) has been proposed to accelerate these tasks. There are several NMP architectures based on multiple memory cubes proposed to improve irregular graph processing applications' performance and energy consumption. Tesseract [3] leverages the large internal bandwidth provided by 16 memory cubes connected in a Dragonfly topology. A single-issue in-order CPU and a prefetcher, serving as computation units, are deployed on the logic layer of each vault. Tesseract adopts Pregel [64] and provides a vertex-centric programming model. The authors report  $9 \times$  speedups relative to a traditional multicore system using out-of-order cores. While this performance gain is substantial, Dai et al. [24] and Zhang et al. [108] indicate that Tesseract's overall memory bandwidth utilization is less than 40%, implying there are additional performance gains to be had. The reason for this bandwidth utilization limit is cross-cube memory accesses, which Tesseract did not try to optimize.

To reduce cross-cube communications, Zhang et al. [108] proposed a graph partitioning method, called *source-cut*. If two or more cross-edges share the same source vertex but have different destination vertices in a common cube, a replica of the source vertex is placed in the destination cube. Therefore, the data of the source vertex need only be transferred once. To realize the source-cut partitioning method, Zhang et al. proposed a *Two-Phase Vertex Programming* model. The GenUpdate phase generates the update for each replica and the ApplyUpdate phase updates each replica. Cross-cube communication will only happen before ApplyUpdate. To hide the remote latency of cross-cube communication, GenUpdate and communication are overlapped asynchronously. A barrier after each phase ensures that hardware cache coherence is not required.

Despite of the promising results of Zhang et al. [108], there are two inherent properties of source-cut partitioning that limits its potential: (1) Since only one cross-cube edge pattern is considered, it only considers a fraction of the cross-cube edges that might potentially be eliminated. (2) It adopts a fixed initial vertex distribution, which limits its options for reducing cross-cube communication overheads. To address these limitations, we introduce a novel software/hardware co-design framework for multi-cube NMP systems, called *SuperCut*, to effectively reduce cross-cube communication overheads while maintaining workload balance.

Besides the comparison baselines of Tesseract and GraphP, there are other NMP architectures designed to accelerate large-scale graph processing. GraphPIM [69] proposes an instruction offloading mechanism to computation units on the logic layer of a single HMC device instead

of a network consisting of multiple cubes. MessageFusion [7] proposes an NMP architecture to reduce cross-cube communication in transit by coalescing multiple cross-cube messages before reaching the same destination vertex. We take inspiration from this technique in our destination-cut static partitioning algorithm. GraphVine [8] explores another way to reduce HMC network congestion at runtime using multicast techniques. Both these works failed to optimize the distribution of vertices, limiting their efficiency. GraphH [24], GraphQ [119] and GraphRing [57] tried to regularize communication overhead by proposing reconfigurable HMC interconnection, a vertex reordering mechanism, and a ring-structured memory network, respectively. None of them directly reduced communication volume or considered graph distribution.

For general distributed graph processing systems, graph partitioning strategies also play a vital role in communication optimization and workload balance, which can be classified [25] into edge-cut and vertex-cut. PowerGraph [36] and PowerLyra [19] adopt vertex-cut to minimize vertex numbers across partitions by assigning edges to replicas in different machines. Although vertex-cut shows good load balance for skewed graphs, it is not suitable for nearmemory graph processing because it leads to higher communication cost and requires more complicated implementation mechanisms. Therefore, the partitioning algorithms designed for near-memory graph processing, including the algorithms proposed in this work, are edge-cut [61, 64, 118] in which vertices of the graph are evenly assigned to minimize the number of edges across partitions. Pregel [64] is an early distributed graph processing system which adopts random edge-cut partitioning and provides the message-passing mechanism to deliver updates between machines. Tesseract adopts this approach. The partitioning proposed in GraphP [108] is also an edge-cut method in essence, in which out-going edges across memory cubes are partitioned. The basic principle of destination-cut partitioning as an edge-cut method where edges sharing a destination are combined has been adopted for traditional systems [36, 118].

In this work, we are interested in its effectiveness on near-memory systems, in which the overheads of a cross-cube data transfer are very different than a message-passing send/receive pair.

### 2.4 Graph Neural Networks

Machine Learning (ML) on graphs has experienced a surge of popularity in the past decade, since traditional ML models, which are designed to process Euclidean data with regular structures, are ineffective at performing prediction tasks on graphs. Due to their simplicity and superior representation learning ability, Graph Neural Networks (GNNs) [29, 49, 90, 103, 107] have achieved impressive performance on various graph learning tasks, such as node classification, graph classification, etc. In this dissertation, we focus on 6 GNN models featuring diverse architectures.

Graph Convolutional Network (GCN) [49] is one of the earliest GNN models and has a simple structure. It updates node features by aggregating neighboring node features and performing linear projection. The formula is given as follows:

$$h_i^{l+1} = \text{ReLU}\left(U^l \sum_{j \in N_i} h_j^l\right)$$

(2.1)

Where  $U^l \in \mathbb{R}^{d \times d}$  is the learnable weight matrix of the linear projection, which performs vector-matrix multiplication.  $h_i^l \in \mathbb{R}^{d \times 1}$  is the feature vector of vertex *i* in layer *l*, and  $N_i$  represents the neighboring vertices of vertex *i*.

GraphSage (GS) [38] introduces an inductive framework to improve the scalability over GCN by aggregating information from the fixed-size set of neighbors via uniform sampling, explicitly incorporating feature vectors of both the target vertex and its source neighbors. The mathematical expression of GraphSage with a mean aggregator is formulated as follows:

$$h_i^{l+1} = \operatorname{ReLU}\left(U^l \operatorname{Concat}\left(h_i^l, \frac{1}{|N_i|} \sum_{j \in N_i} h_j^l\right)\right)$$

$$= \operatorname{ReLU}\left(V^l h_i^l + W^l \frac{1}{|N_i|} \sum_{j \in N_i} h_j^l\right)$$

(2.2)

Where  $N_i$  is the set of source neighbors of vertex i, and  $h_i^l \in \mathbb{R}^{d \times 1}$  is the feature vector of vertex i in layer l. The learnable weight matrix of the linear projection,  $U^l \in \mathbb{R}^{d \times 2d}$ , is stored in on-chip memory. Given that distinct weight parameters are used for the target vertex and

source neighbors,  $U^l$  is divided into  $V^l \in \mathbb{R}^{d \times d}$  and  $W^l \in \mathbb{R}^{d \times d}$ , enabling parallel execution of both paths to hide the latency of linear projection for the target vertex.

Graph Isomorphism Network (GIN) [103] employs the Weisfeiler-Lehman Isomorphism Test [96] as its foundation to investigate the discriminative ability of GNNs. The formula of GIN is described as follows:

$$h_i^{l+1} = \operatorname{ReLU}\left(U^l \operatorname{ReLU}\left(V^l \left((1+\epsilon)h_i^l + \sum_{j\in N_i} h_j^l\right)\right)\right)$$

(2.3)

where  $\epsilon$  is a learnable scalar weight,  $U^l$  and  $V^l \in \mathbb{R}^{d \times d}$  denote learnable weight matrices of cascaded VMM modules,  $h_i^l \in \mathbb{R}^{d \times 1}$  again refers to the feature vector of vertex i in layer l, and  $N_i$  is again the source neighbors of vertex i.

Graph Attention Network (GAT) [90] is an anisotopic GNN model that uses self-attention mechanisms to weight and learn representations of neighbor vertices unequally. The equation is described as follows:

$$h_i^{l+1} = \operatorname{Concat}_{k=1}^K \left( \operatorname{ELU}\left(\sum_{j \in N_i} \alpha_{ij}^{k,l} U^{k,l} h_j^l\right) \right)$$

(2.4)

$$\alpha_{ij}^{k,l} = \text{Softmax}(e_{ij}^{k,l}) = \frac{\exp(e_{ij}^{k,l})}{\sum_{j' \in N_i} \exp(e_{ij'}^{k,l})}$$

(2.5)

$$e_{ij}^{k,l} = \text{LeakyReLU}(\vec{a}^T Concat(U^{k,l}h_i^l, U^{k,l}h_j^l))$$

= LeakyReLU $(a_{src}^{k,l}U^{k,l}h_i^l + a_{dest}^{k,l}U^{k,l}h_j^l)$  (2.6)

where  $\alpha_{ij}^l \in \mathbb{R}^K$  is the attention score between vertex *i* and vertex *j* of layer *l*,  $U^{k,l} \in \mathbb{R}^{d \times d}$ and  $\vec{a} \in \mathbb{R}^{2d}$  are learnable parameters. Note that the weight parameter  $\vec{a}^T$  is decomposed into  $a_{src}^l$  and  $a_{dest}^l \in \mathbb{R}^d$  in the DGL library, because it is more efficient in terms of performance and memory footprint by transferring VMM between  $U^{k,l}$  and  $h^l$  from edge-wise to node-wise operations, especially for sparse graphs where the edge number is larger than the vertex number. Mixture Model Networks (MoNet, MN) [68] is a general anisotopic GNN framework designed for graph and node classification tasks using Bayesian Gaussian Mixture Model (GMM) [27]. The model is formulated as follow:

$$h_i^{l+1} = \text{ReLU}\left(\sum_{k=1}^K \sum_{j \in N_i} w_k(u_{ij}) U^{k,l} h_j^l\right)$$

$$= \text{ReLU}\left(\sum_{k=1}^K U^{k,l} \sum_{j \in N_i} w_k(u_{ij}) h_j^l\right)$$

(2.7)

$$w_k(u_{ij}) = \exp\left(-\frac{1}{2}(u_{ij}^l - \mu_k^l)^T (\sum_{k}^l)^{-1} (u_{ij}^l - \mu_k^l)\right)$$

(2.8)

$$u_{ij}^{l} = \operatorname{Tanh}(V^{l}pseudo_{ij}^{l} + v^{l})$$

(2.9)

$$pseudo_{ij}^{l} = \text{Concat}(deg_i^{-0.5}, deg_j^{0.5})$$

$$(2.10)$$

where  $v^l \in \mathbb{R}^2$ ,  $V^l \in \mathbb{R}^{2 \times 2}$ ,  $\mu \in \mathbb{R}^{K \times 2}$ ,  $(\sum_k^l)^{-1} \in \mathbb{R}^{K \times 2}$ , and  $U^l \in \mathbb{R}^{d \times d}$  are learnable parameters of GMM.  $v^l$  and  $V^l$  represent the pseudo-coordinates between the target vertex and its neighbors,  $\mu \in \mathbb{R}^{K \times 2}$  and  $(\sum_k^l)^{-1} \in \mathbb{R}^{K \times 2}$  denote the mean vector and covariance matrix.  $U^{k,l}$  is the weight matrix.

The Gated Graph ConvNet (GatedGCN, GGCN) [13] is a type of anisotropic graph neural network model that employs a gating mechanism to regulate the flow of information during message passing, allowing the model to emphasize relevant information and filter out irrelevant one. The gating mechanism utilizes gate functions (e.g., sigmoid) to control the flow of messages at each layer. The mathematical expression for GatedGCN is provided below:

$$h_{i}^{l+1} = \text{ReLU}\left(A^{l}h_{i}^{l} + \frac{\sum_{j' \in N_{i}} B^{l}h_{j'}^{l} \odot \sigma(e_{ij'}^{l+1})}{\sum_{j' \in N_{i}} \sigma(e_{ij'}^{l+1}) + \epsilon}\right)$$

(2.11)

$$e_{ij}^{l+1} = E^l h_i^l + D^l h_j^l + C^l e_{ij}^l$$

(2.12)

where  $A^l$ ,  $B^l$ ,  $D^l$ ,  $E^l$  and  $C^l \in \mathbb{R}^{d \times d}$  are learnable matrix parameters,  $e_{ij}^l \in \mathbb{R}^{1 \times d}$  denote the edge features from vertex *i* to *j* layer *l*,  $h_i^l$  represents node features of vertex *i* in layer *l*,  $\odot$  denotes Hadamard product,  $\sigma$  denotes the sigmoid function, and  $\epsilon$  is a constant for numerical stability.

### 2.5 High-Level Synthesis

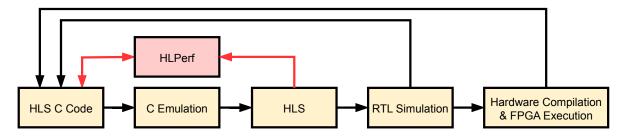

The basics of a High-Level Synthesis (HLS) workflow, which is adopted by most of the mainstream HLS tools, such as Xilinx Vitis and Intel OpenCL HLS, is illustrated in Figure 2.3. In the dissertation, we use Xilinx Vitis [4] as the running example, but the underlying principles are the same for many other HLS tools. It contains the following steps.

Figure 2.3: Conventional HLS workflow (in black) and our contribution (in red).

(1) HLS C Code: HLS users are first required to build HLS kernels based on target algorithms using high-level languages (e.g., HLS C) annotated with pragmas that can have substantial impact on the final performance. Among all the various optimization techniques, **#pragma HLS dataflow** is frequently first used to build a dataflow architecture in which all the functions in the dataflow scope are connected by FIFOs to form a pipeline-style architecture and scheduled to be performed concurrently. In our GNN applications, each function contains one or more loops. Then they use other pragmas such as Pipeline, Loop Unroll, Loop Merge, Burst Memory Access, Memory Port Widening, etc., to optimize each function or loop in terms of throughput, iteration, and memory accesses. In addition, distinct coding paradigms with the same functionality can also influence the final performance of the HLS kernel.

(2) **C** Emulation: The HLS kernel file, along with the host file, configuration files, and input dataset are compiled and executed under software emulation mode. Note that C emulation only focuses on functionality verification of the HLS kernel. Thus, it doesn't involve performance estimation.

(3) **High-Level Synthesis**: In this step, HLS tools convert the HLS Kernel from the high-level C-like description to an RTL-level hardware description language (e.g., Verilog, VHDL).

To achieve this goal, the HLS tool initially preprocesses the source code of the HLS kernel and conducts transformations based on user-defined pragmas. Subsequently, operations are scheduled in accordance with the corresponding dependency and optimization techniques, and then bound to hardware resources. After this process, coarse-grained control flows are typically implemented as finite-state machines, while fine-grained instruction collections are realized as variants of pipelines. Following these steps, the HLS tool provides estimated intermediate results of the scheduling such as the latency and throughput of pipelines. Finally, RTL code is generated. Note that due to the inherent dynamic characteristics of GNN applications and their significant dependence on input graph datasets, the HLS tool is incapable of providing conclusive outcomes through static performance estimation.

(4) **RTL Simulation**: To obtain estimated cycle-accurate performance results of HLS kernels, the generated RTL code, along with host files, configuration files, and graph datasets, are compiled and executed under hardware emulation mode for RTL simulation. Due to the inherent irregularity of GNNs and graph datasets, the simulation needs to include at least a representative subset of the input graphs to be processed. The results are stored in a waveform file containing cycle-accurate transitions of all the signals in the RTL code. To debug or improve the performance of the HLS kernels, users are required to trace these RTL signals (often with incomprehensible names) back to HLS code, modify the HLS code, and repeat the procedure until the performance goals are satisfied. However, the whole procedure takes a significant amount of time due to the incorporation of extensive architectural details and the desire to be cycle accurate. Consequently, RTL simulation is usually impractical to be used for estimating the performance of complicated GNN HLS kernels with large-scale graph datasets.

(5) Hardware Compilation & FPGA Execution: To get the physical layout, the generated RTL code is converted into a gate-level representation (i.e., netlist) for a specific architecture and then mapped to specific locations of the target device via the place & route process. A series of back-end strategies on physical implementations are performed to get a trade-off among design's performance, area, and power. The finalized circuit description is encapsulated into a bitstream file, which is then executed on an FPGA, enabling the measurement of the actual execution times. This step is quite time consuming (e.g., 4.5-12 hours for compilation of GNN HLS kernels), and even though direct execution is clearly the gold standard for performance understanding, it is the length of these build times that makes the inclusion of direct execution in the iterative design cycle unattractive.

Although HLS bridges the gap between software and hardware development, optimizing HLS codes is substantially distinct from conventional software programming. In fact, due to the FPGAs' inherent attributes, such as lack of built-in cache mechanisms, low clock frequency (relative to traditional processor cores), and fine-grained configurability, the performance difference between a well-optimized version and naive version of the same kernel can be two or three orders of magnitude [15, 32, 85]. Therefore, to achieve the best performance, HLS developers need to explore a large optimization space for HLS designs with various optimization pragmas, coding paradigms, etc. As the complexity of kernels increases, optimizing (or auto-optimizing) such kernels is difficult via conventional HLS workflows.

To address the performance evaluation challenge, several works have been proposed, which can be classified into 2 main classes: static estimation [18, 23, 26, 63] and cycle-accurate simulation [1, 22, 79]. Static estimation is performed at compile time so has difficulty with performance that is input dependent, and cycle-accurate simulation substantially accelerates the speed of RTL-level simulation while maintaining quality of the performance predictions. We will report research happening in each area in turn.

Legup [18] estimates the speedup of the accelerated function in the HLS kernel in the straightforward way of multiplying the number of iterations recorded by software profiling tools and the single-iteration execution time extracted from RTL simulation. This method does depend on RTL simulation. Additionally, it assumes the FPGA algorithms are performed sequentially, so it doesn't consider a number of HLS optimization techniques, such as pipelined execution. HLScope+ [23] proposes a method to perform pipelined loop analysis by inserting hooks to HLS C code and extracting HLS abstraction information. However, it fails to capture the irregularity of data sets (e.g., graph topologies) and respond to the dynamic properties of irregular algorithms and HLS kernels. Pyramid [63] uses machine learning techniques to estimate both FPGA area requirements and achievable clock rates. De Fine Licht et al. [26] propose a static expression for pipelined loop analysis with some optimization techniques. However, it is also not sufficient for irregular data and algorithms.

On the other hand, Flash [22] uses scheduling information to build a C cycle-accurate simulation model. FastSim [1] translates generated RTL code to an equivalent C++ cycle-accurate model. LightningSim [79] proposes a LLVM-IR-trace-based method to reconstruct a cycle-accurate model. In spite of the ability of these cycle-accurate methods to analyze the dynamic behavior of many FPGA algorithms, there are still some drawbacks: (1) These works

are designed to provide both functional correctness verification and performance estimation, increasing the workload of the evaluation process. (2) Since these methods are related to the construction and execution of cycle-accurate time models with many low-level details, the simulation speed is limited.

Design space search and custom architectures aimed specifically at GNNs have also received attention recently [35, 39, 58, 59, 104, 109, 116, 117]. HGNAS [116, 117] targets edge devices for execution of GNNs, explicitly considering reduction in memory requirements as well as execution speed. DeepBurning-GL [58] proposes an automated framework to convert specific component of GNN models based on DGL to RTL codes using pre-defined hardware templates. G-CoS [109] works to match GNN structure with the available execution platform(s), and Hao et al. [39] exploit reinforcement learning as part of the design space search. HyGCN [104] is a custom ASIC design aimed at graph neural network inference that is evaluated using the TSMC 12 nm CMOS process. EnGN [59] targets the need to scale up to large graphs by introducing a ring-edge-reduce dataflow to handle graphs with arbitrary dimensions. AWB-GCN [35] is a custom FPGA design that addresses the variability in graph topology by auto-tuning the accelerator during the execution of the GNN application itself. While the authors of all of the above studies evaluate performance on a variety of graphs, none of the design space exploration investigations incorporated simulation into the performance evaluation that specifically guides the search of the design space, and only AWB-GCN has explicit mechanisms for adapting to variations in properties of the input graphs. Our intention is to make simulation sufficiently fast that it can be seriously considered in an automated design space search context.

GNN models are but one example of applications that execute on graphs. Chen et al. [20] introduce ThunderGP, a framework for developing general graph applications for deployment on FPGAs. ThunderGP uses a dataflow architecture for its designs, so a GNN model developed using ThunderGP could likely utilize HLPerf as a companion performance evaluation tool.

We are interested in the effectiveness of modern HLS tools to accelerate GNN inference, and the availability of fast, high-quality understanding of the performance implications of the design choices that are made in the HLS optimization task.

## Chapter 3

# Executing Data Integration Near the Memory

According to profiling results presented in the data integration benchmark suite (DIBS) [17], the fraction of data movement instructions are more than 50% in 8 of 12 data integration workloads, implying a strong sensitivity to the architecture of the memory subsystem and opportunities to reduce expensive data movement with near-memory processing techniques. Meanwhile, since data integration workloads are embarrassingly parallel, targeting at every independent data individual in the stream, data parallelism provided by NMP architecture is potentially beneficial as performance scales with large numbers of NMP cores. Here, we propose the question: *To what extent does NMP benefit data integration applications?*

## 3.1 Workload Characterization

To answer the question, We characterize these DIBS workloads using four metrics: temporal locality, spatial locality, memory access rate, and arithmetic instruction rate. These workloads have a high degree of data movement, motivating the emphasis on memory in the application characterization.

Temporal and spatial locality are quantified using the techniques proposed by Weinberg et al. [95]. Each locality score is on a normalized range [0,1], with higher scores indicating a greater degree of locality.

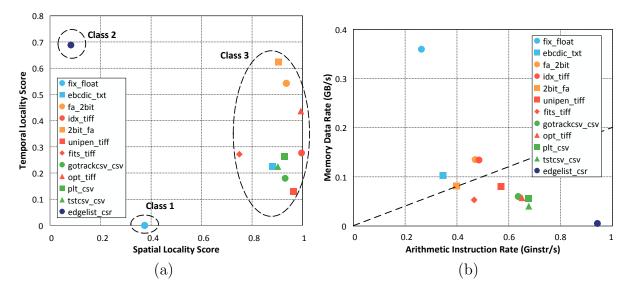

Figure 3.1(a) shows the temporal and spatial locality of each of the DIBS applications. We classify the applications into 3 classes: (1) low spatial and low temporal locality, (2) low spatial and high temporal locality, and (3) high spatial locality.

Figure 3.1: Workload characterization of data integration workloads. (a) Temporal and spatial locality scores. (b) Memory data rate vs. arithmetic instruction rate.

The fix\_float application, with relatively low spatial locality and lowest temporal locality belongs to class 1. Others have shown that this type of workload can benefit from near-memory processing techniques, e.g., see [83].

The edgelist\_csr application, with low spatial locality and high temporal locality, belongs to class 2. In this case, the high temporal locality implies that a deep cache hierarchy can benefit performance, so it might not do as well on a near-memory architecture.

The remaining 10 out of the 12 applications, belonging to class 3 with high spatial locality, lie at the right of Figure 3.1(a). These locality scores give mixed signals as to the suitability of these workloads for near-memory processing techniques.

We measure the memory accesses and arithmetic instructions to further characterize our data integration workloads. In addition, we will discuss this characterization in terms of their ratio, which we call the *memory/ops* ratio.