#### Washington University in St. Louis Washington University Open Scholarship

All Theses and Dissertations (ETDs)

January 2010

# Parallelization of dynamic programming recurrences in computational biology

Arpith Jacob Washington University in St. Louis

Follow this and additional works at: https://openscholarship.wustl.edu/etd

#### **Recommended Citation**

Jacob, Arpith, "Parallelization of dynamic programming recurrences in computational biology" (2010). *All Theses and Dissertations (ETDs)*. 169. https://openscholarship.wustl.edu/etd/169

This Dissertation is brought to you for free and open access by Washington University Open Scholarship. It has been accepted for inclusion in All Theses and Dissertations (ETDs) by an authorized administrator of Washington University Open Scholarship. For more information, please contact digital@wumail.wustl.edu.

#### WASHINGTON UNIVERSITY IN ST. LOUIS

School of Engineering and Applied Science Department of Computer Science and Engineering

> Thesis Examination Committee: Jeremy Buhler, Chair Michael Brent Ron Cytron Mark Franklin Robert Morley Bill Smart David Taylor

### PARALLELIZATION OF DYNAMIC PROGRAMMING RECURRENCES IN COMPUTATIONAL BIOLOGY

by

Arpith Chacko Jacob

A dissertation presented to the Graduate School of Arts and Sciences of Washington University in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

December 2010 Saint Louis, Missouri copyright by Arpith Chacko Jacob 2010

#### ABSTRACT OF THE THESIS

Parallelization of dynamic programming recurrences in computational biology by

Arpith Chacko Jacob Doctor of Philosophy in Computer Science Washington University in St. Louis, 2010 Research Advisor: Professor Jeremy Buhler

The rapid growth of biosequence databases over the last decade has led to a performance bottleneck in the applications analyzing them. In particular, over the last five years DNA sequencing capacity of next-generation sequencers has been doubling every six months as costs have plummeted. The data produced by these sequencers is overwhelming traditional compute systems. We believe that in the future compute performance, not sequencing, will become the bottleneck in advancing genome science.

In this work, we investigate novel computing platforms to accelerate dynamic programming algorithms, which are popular in bioinformatics workloads. We study algorithm-specific hardware architectures that exploit fine-grained parallelism in dynamic programming kernels using field-programmable gate arrays (FPGAs). We advocate a high-level synthesis approach, using the recurrence equation abstraction to represent dynamic programming and polyhedral analysis to exploit parallelism. We suggest a novel technique within the polyhedral model to optimize for throughput by pipelining independent computations on an array. This design technique improves on the state of the art, which builds latency-optimal arrays. We also suggest a method to dynamically switch between a family of designs using FPGA reconfiguration to achieve a significant performance boost. We have used polyhedral methods to parallelize the Nussinov RNA folding algorithm to build a family of accelerators that can trade resources for parallelism and are between 15-130x faster than a modern dual core CPU implementation. A Zuker RNA folding accelerator we built on a single workstation with four Xilinx Virtex 4 FPGAs outperforms 198 3 GHz Intel Core 2 Duo processors. Furthermore, our design running on a single FPGA is an order of magnitude faster than competing implementations on similar-generation FPGAs and graphics processors.

Our work is a step toward the goal of automated synthesis of hardware accelerators for dynamic programming algorithms.

### Acknowledgments

I am deeply indebted to my advisor Dr. Jeremy Buhler, who has patiently guided me through my entire graduate career. I am thankful for the hours of discussions, all the comments and suggestions, and for helping me successfully reach this stage in my career. I would like to thank Dr. Buhler for taking a chance on me all these years ago, and for his continued support through the "known unknowns" and the "unknown unknowns." Dr. Buhler has spent countless hours reviewing and perfecting my work. I am eternally grateful for your support.

I would like to thank Dr. Roger Chamberlain with whom I have also worked closely during my entire graduate career. I am extremely grateful for his confidence in me and the many hours spent helping me improve my work. Dr. Buhler and Dr. Chamberlain have always afforded me great independence, and even played along with some of my crazier ideas. You have taught me how to do research and I have thoroughly enjoyed working with both of you.

I am extremely grateful for financial support provided by an NIH award R42 HG003225 and an ACM/IEEE-CS HPC Ph.D. fellowship in 2007. This support allowed me to focus entirely on my research.

I would like to thank members of my committee: Dr. Mark Franklin, Dr. Ron Cytron, Dr. Michael Brent, Dr. Bill Smart, Dr. Robert Morley, and Dr. David Taylor. You have asked the hard questions and forced me to consider my research in the larger context. In particular, I would like to thank Dr. Franklin, who showed me the importance of communicating research results through the (always merciless, sometimes frustrating) culling of technical detail in presentations. Thank you all for sacrificing your valuable time for me.

I would like to thank members past and present of the High Performance Computational Biology group at Washington University. Special thanks to Joseph Lancaster with whom I have worked for the last six years. I am especially grateful for your patience in the early years as I came to grips with the world of hardware programming—I can only imagine how frustrating I might have been! I would also like to thank Praveen Krishnamurthy, Eric Tyson, Brandon Harris, Peng Li, Lin Ma, Rahav Dor, and Jwalant Ahir for the pleasant work environment you created. I would also like to thank Hongtao Sun and Stephen Cole for many enjoyable interactions.

I spent a summer doing an internship with Dr. Maya Gokhale at the Lawrence Livermore National Laboratory. I was able to learn a great deal from her perspective on reconfigurable computing and she has helped my career a great deal.

Exegy Inc., provided the FPGA system we used in this dissertation. Their (relatively easy to use) platform and gracious support was critical in achieving the results in this dissertation. In particular, I would like to thank Mr. Berkely Shands who has patiently answered all my questions on using the system.

I would like to acknowledge the enormous support of the staff members of the computer science department. Your efficiency in dealing with administrative concerns and the congenial environment in the department is much appreciated.

I would like to thank members of International Friends who have provided community during the last six years.

Finally, I would like to thank my Father and Mother who along with my brother have been unceasing in their support and encouragement throughout my life. I dedicate this work to my family.

Arpith Chacko Jacob

Washington University in Saint Louis December 2010 Unless the LORD builds the house,

its builders labor in vain.

Unless the LORD watches over the city,

the watchmen stand guard in vain.

In vain you rise early

and stay up late,

toiling for food to eat—

for He grants sleep to those He loves.

Psalm 127:1-2

He named it Ebenezer, saying, "Thus far has the LORD helped us." 1 Samuel 7:12b

## Contents

| Abstract     |       |                                                                                                               |           |  |

|--------------|-------|---------------------------------------------------------------------------------------------------------------|-----------|--|

| $\mathbf{A}$ | ckno  | wledgments                                                                                                    | iv        |  |

| Li           | st of | Tables   ····································                                                                 | x         |  |

| Li           | st of | Figures                                                                                                       | xii       |  |

| 1            |       | roduction                                                                                                     | 1         |  |

|              | 1.1   | Dynamic Programming in Computational Biology                                                                  | 2         |  |

|              | 1.2   | A Bottleneck in Computational Biology Analysis                                                                | 5         |  |

|              | 1.3   | Rise of Non-traditional Computing Architectures                                                               | 12        |  |

|              | 1.4   | Challenges of Development in Hardware Languages                                                               | 17        |  |

|              | 1.5   | A New Approach to an Old Problem                                                                              | 19        |  |

|              | 1.6   | Dissertation Overview                                                                                         | 20        |  |

|              |       | 1.6.1 Brief Background                                                                                        | 21        |  |

|              |       | 1.6.2 Summary of our Approach                                                                                 | 22        |  |

|              |       | 1.6.3 Research Questions                                                                                      | 26        |  |

|              |       | 1.6.4 Contributions $\ldots$ | 27        |  |

|              |       | 1.6.5 Outline                                                                                                 | 30        |  |

| <b>2</b>     | Rel   | ated Work                                                                                                     | 32        |  |

|              | 2.1   | High-Level Code-Generation Tools for Computational Biology                                                    | 34        |  |

|              | 2.2   | High-Level Hardware Synthesis Tools for Computational Biology                                                 | 39        |  |

|              | 2.3   | High-Level Synthesis Tools for Recurrence Equations                                                           | 40        |  |

| 3            | Bac   | kground: Parallelization of Dynamic Programming                                                               | <b>43</b> |  |

|              | 3.1   | Dynamic Programming                                                                                           | 43        |  |

|              | 3.2   | Systolic Arrays                                                                                               | 44        |  |

|              |       | 3.2.1 History of Systolic Arrays                                                                              | 45        |  |

|              | 3.3   | Systems of Recurrence Equations                                                                               | 46        |  |

|              | 3.4   | Dynamic Programming as Systems of Affine Recurrence Equations                                                 | 48        |  |

|              |       | 3.4.1 Classification of Dynamic Programming                                                                   | 49        |  |

|              | 3.5   | Systolic Arrays as Systems of Uniform Recurrence Equations                                                    | 50        |  |

|              | 3.6   | Parallelization of Uniform Recurrences                                                                        | 52        |  |

|              | 0.0   | 3.6.1 Preliminaries of the Polyhedral Representation                                                          | 53        |  |

|              |       | 3.6.2 Array Mappings for Recurrence Equations                                                                 | 54        |  |

|              |       | s.s.2 milling mappings for recurrence Equations                                                               | 04        |  |

|          |            | 3.6.3 Latency-Space Optimal Array Mappings                    | 56  |

|----------|------------|---------------------------------------------------------------|-----|

|          |            | 3.6.4 Localization                                            | 59  |

|          | 3.7        | Summary                                                       | 63  |

| 4        | Acc        | elerating the Nussinov RNA Folding Recurrence                 | 64  |

|          | 4.1        | The Nussinov Algorithm                                        | 66  |

|          | 4.2        | Parallelizing Nussinov                                        | 68  |

|          |            | 4.2.1 Pipelining Affine Dependencies                          | 69  |

|          |            | 4.2.2 Deriving Full-Size Arrays                               | 73  |

|          | 4.3        | PE Precision and Smaller Inputs                               | 76  |

|          | 4.4        | Evaluation                                                    | 77  |

|          |            | 4.4.1 Software Baseline                                       | 77  |

|          |            | 4.4.2 Hardware Baseline                                       | 77  |

|          |            | 4.4.3 Results                                                 | 78  |

|          | 4.5        | Related Work                                                  | 80  |

|          | 4.6        | Conclusions                                                   | 80  |

|          | _          |                                                               |     |

| <b>5</b> |            | ign Space Exploration of Throughput-optimized Arrays          | 81  |

|          | 5.1        | Recapitulation of Background                                  | 83  |

|          | 5.2        | Motivating Examples                                           | 84  |

|          | 5.3        | Characterizing Throughput-optimized Arrays                    | 85  |

|          |            | 5.3.1 A Design Criterion for Throughput Optimality            | 87  |

|          | <b>-</b> , | 5.3.2 Implications for Design-Space Exploration               | 90  |

|          | 5.4        | Finding Throughput-Optimized Projection Vectors               | 91  |

|          |            | 5.4.1 A Search Procedure for Projection Vectors               | 92  |

|          |            | 5.4.2 Basic Definitions for Bounds                            | 93  |

|          |            | 5.4.3 Search Complexity and Application to Examples           | 97  |

|          | 5.5        | Selecting Schedules to Support Retiming                       | 99  |

|          | 5.6        | Software Tool                                                 | 101 |

|          | 5.7        | Results                                                       | 101 |

|          | 5.8        | Related Work                                                  | 108 |

|          | 5.9        | Conclusion                                                    | 110 |

| 6        | Res        | ource-limited Array Mappings                                  | 111 |

|          | 6.1        | Generating 1-D and 2-D Arrays                                 | 112 |

|          |            | 6.1.1 A 1-D Array for Nussinov                                | 113 |

|          | 6.2        | Partitioned Arrays                                            | 114 |

|          |            | 6.2.1 A Partitioned 1-D Array for Nussinov                    | 117 |

|          |            | 6.2.2 A Partitioned 2-D Array for Nussinov                    | 120 |

|          | 6.3        | Evaluation                                                    | 122 |

|          | 6.4        | Conclusions                                                   | 129 |

| 7        | Opt        | imal Runtime Reconfiguration Strategies for Systolic Arrays . | 131 |

viii

|                           | 7.1   | Selecting an Optimal Set of Arrays                          | 133 |

|---------------------------|-------|-------------------------------------------------------------|-----|

|                           | 7.2   | Application to RNA Folding                                  | 134 |

|                           | 7.3   | Results                                                     | 136 |

|                           |       | 7.3.1 Folding Pyrosequencing Reads                          | 137 |

|                           |       | 7.3.2 Restricting the Number of Arrays                      | 140 |

|                           |       | 7.3.3 Folding Long Reads                                    | 141 |

|                           | 7.4   | Related Work                                                | 144 |

|                           | 7.5   | Conclusion                                                  | 145 |

| 8                         | Ana   | alysis and Acceleration of the Zuker RNA Folding Recurrence | 146 |

|                           | 8.1   | The Zuker Recurrence                                        | 147 |

|                           | 8.2   | Parallelizing Zuker                                         | 150 |

|                           |       | 8.2.1 Handling Free Energy Scores                           | 150 |

|                           |       | 8.2.2 1-D Zuker Array                                       | 160 |

|                           | 8.3   | Evaluation                                                  | 163 |

|                           |       | 8.3.1 Techniques for Synthesis After Polyhedral Analysis    | 163 |

|                           |       | 8.3.2 Results for the Zuker Array                           | 164 |

|                           | 8.4   | Related Work                                                | 167 |

|                           |       | 8.4.1 Multi-core Implementations                            | 167 |

|                           |       | 8.4.2 RNA Folding on GPUs                                   | 169 |

|                           |       | 8.4.3 FPGA Implementations                                  | 169 |

|                           | 8.5   | Conclusions                                                 | 173 |

| 9                         | Con   | clusions & Future Directions                                | 174 |

|                           | 9.1   | Observations & Comments                                     | 176 |

|                           | 9.2   | Future Work                                                 | 178 |

|                           |       | 9.2.1 Short-term goals                                      | 178 |

|                           |       | 9.2.2 Long-term goals                                       | 179 |

| $\mathbf{A}_{\mathbf{j}}$ |       | dix A A Survey of Dynamic Programming in Computationa       |     |

|                           | Bio   | $\log y$                                                    | 182 |

| Re                        | efere | nces                                                        | 190 |

# List of Tables

| 1.1                                       | A compilation of dynamic programming algorithms from computa-<br>tional biology. A detailed description of these algorithms, including<br>the time and space growth functions, are in Appendix A. Legend for<br>Accelerators: F - FPGA, G - GPU, CB - IBM Cell broadband, S -<br>SIMD extensions on a workstation, CL - Cluster of workstations                                                                              | 3                 |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 4.1<br>4.2<br>4.3                         | Comparison of the two full-size Nussinov systolic arrays Variation of array FS-B's resource usage with PE precision Speedup of Nussinov arrays vs. modern x86 CPU. Runtimes are measured in seconds                                                                                                                                                                                                                          | 78<br>78<br>79    |

| 5.1<br>5.2                                | Throughput-area tradeoff for banded Smith-Waterman. Bounding was based on sequences of length $N_0 = 300$ and a band width of $w = 66$ , forcing $ \mathbf{u}  \leq 22$ . The throughput of an array is given by $\frac{1}{\beta}$ where $\beta = 1 + (k_{max} - 1)\gamma$                                                                                                                                                   | 102<br>102        |

| 6.1                                       | Summary of three full-size and resource-constrained arrays for the Nussinov DP recurrence. The table lists the number of processing elements instantiated by each array to fold an RNA of length $N$ , the amount of memory words required in each PE, and the pipelining period. A lower pipelining period equates to a faster array. The parameters $W_j$ and $W_k$ are tile widths as described in the previous sections. | 123               |

| $\begin{array}{c} 6.2 \\ 6.3 \end{array}$ | Speedups of the Nussinov partitioned 2-D array for various RNA lengths.<br>Speedups of the Nussinov unpartitioned 1-D array for various RNA                                                                                                                                                                                                                                                                                  |                   |

| 6.4<br>6.5                                | lengths                                                                                                                                                                                                                                                                                                                                                                                                                      | 127<br>127<br>129 |

| 7.1                                       | Full-size arrays for Nussinov recurrence                                                                                                                                                                                                                                                                                                                                                                                     | 135               |

| 8.1                                       | Area report of processors in our array. The three rows represent num-<br>ber of LUTs used as shift registers for delays, number of LUTs for<br>arithmetic, and number of block RAMs                                                                                                                                                                                                                                          | 166               |

| 8.2 | Performance of the Zuker design folding 1 million randomly generated |     |

|-----|----------------------------------------------------------------------|-----|

|     | RNAs of length 267 on a multi-FPGA system. The hardware arrays       |     |

|     | were synthesized at 130 MHz.                                         | 166 |

# List of Figures

| 1.1  | A <i>filter</i> computes the score of inputs using a DP kernel and discards  |    |

|------|------------------------------------------------------------------------------|----|

|      | those that do not cross a threshold. As a result, finding the score of       |    |

|      | the optimal solution using DP is more important than the state path          |    |

|      | that leads to the solution.                                                  | 2  |

| 1.2  | The growth of biosequence databases is straining computational anal-         |    |

|      | ysis pipelines.                                                              | 5  |

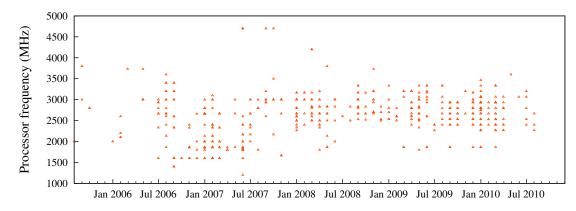

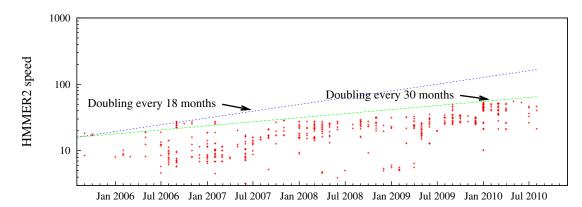

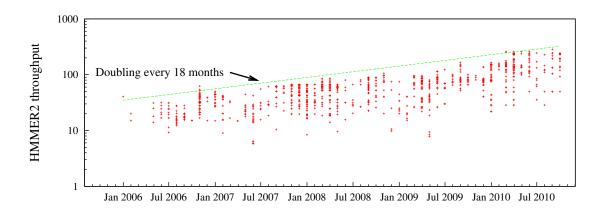

| 1.3  | The two graphs plot historical trends of processor frequency and HMMER2      |    |

|      | speed improvement. Only single chip (socket) systems from SPEC               |    |

|      | CPU2006 are included; however, each chip may have multiple cores             | 7  |

| 1.4  | HMMER2 throughput measured on various multicore workstations us-             |    |

|      | ing Swiss-Prot version 41 as the database. This is a measure of perfor-      |    |

|      | mance assuming that the sequence database does not grow in size              | 8  |

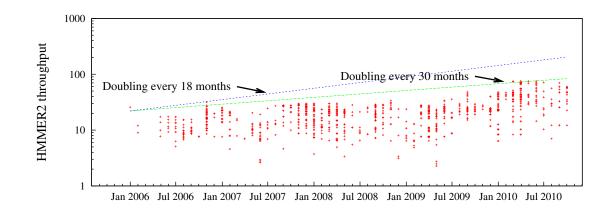

| 1.5  | HMMER2 throughput adjusted for growth of the Swiss-Prot database.            |    |

|      | Throughput is now seen to be doubling only every 30 months                   | 9  |

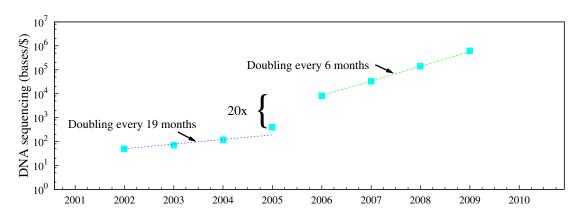

| 1.6  | The graph plots bases sequenced per unit cost as a function of time. We      |    |

|      | draw two important conclusions: a) sequencing costs are falling rapidly,     |    |

|      | while compute performance is only tracking Moore's law, and b) a $20 \times$ |    |

|      | improvement in bases sequenced per unit cost formed a chasm between          |    |

|      | the pre- and post-NGS eras that is yet to be bridged by advances             |    |

|      | in compute performance. Cost for sequencing was made available by            |    |

|      | Stein [140].                                                                 | 9  |

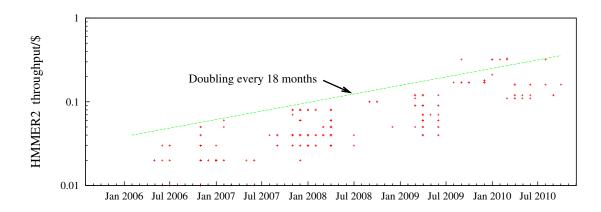

| 1.7  | Historical growth of HMMER2 throughput per dollar on state-of-the-           |    |

|      | art general-purpose processors                                               | 1  |

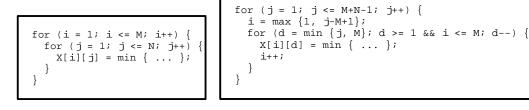

| 1.8  | Two implementations of the Smith-Waterman algorithm in a C-like              |    |

|      | high-level hardware description language                                     | 8  |

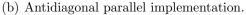

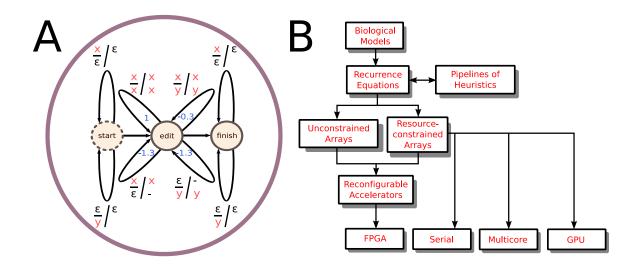

| 1.9  | Overview of the research conducted in this dissertation, which trans-        |    |

|      | forms dynamic programming algorithms into special-purpose accelera-          |    |

|      | tors                                                                         | 23 |

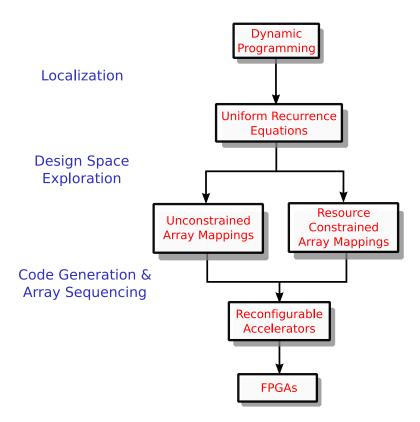

| 1.10 | Three performance criteria that may be optimized when building cus-          |    |

|      | tomized hardware accelerators for a DP kernel. Selecting one of the          |    |

|      | three branches affects the amount of parallelism exploited and the re-       |    |

|      | sources consumed                                                             | 25 |

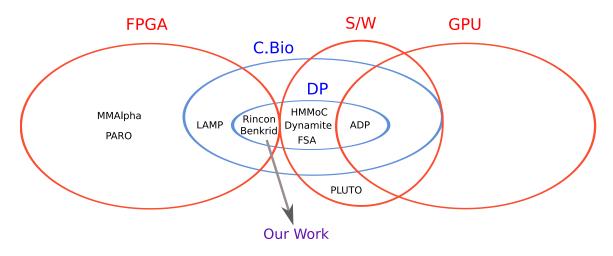

| 2.1                                                                         | A Venn diagram documenting the relationships among related projects<br>surveyed in this chapter. We are interested in tools that generate se-                                                                                                                                                                                                                                                         |                                                                        |

|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

|                                                                             | rial or parallel code for dynamic programming algorithms in compu-<br>tational biology. Here we consider FPGA, GPU, and multi-core accel-                                                                                                                                                                                                                                                             |                                                                        |

|                                                                             | erators. Three works–MMAlpha, PARO, and PLUTO–target general recurrence equations, rather than computational biology specifically,                                                                                                                                                                                                                                                                    |                                                                        |

|                                                                             | but are included for their significance                                                                                                                                                                                                                                                                                                                                                               | 33                                                                     |

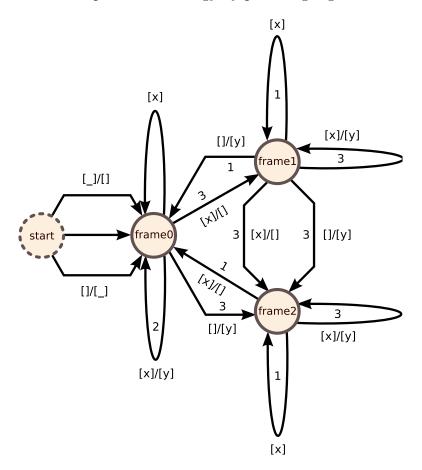

| 2.2                                                                         | A frame maintenance aligner represented by a weighted finite-state ma-                                                                                                                                                                                                                                                                                                                                |                                                                        |

|                                                                             | chine is entered graphically into the visual programming environment developed by Searls and Murphy [135]. The figure is taken from that                                                                                                                                                                                                                                                              |                                                                        |

| 0.0                                                                         | paper                                                                                                                                                                                                                                                                                                                                                                                                 | 34                                                                     |

| 2.3                                                                         | Code for the Smith-Waterman alignment algorithm in the Dynamite<br>language. Note the use of the keyword <i>state</i> to represent recurrence                                                                                                                                                                                                                                                         |                                                                        |

|                                                                             | variables, <i>source</i> to indicate dependencies, and keywords <i>offi</i> and <i>offj</i> to specify dependency offsets. Only two-dimensional recurrences can                                                                                                                                                                                                                                       |                                                                        |

|                                                                             | be expressed in Dynamite. The example is taken from [20]                                                                                                                                                                                                                                                                                                                                              | 36                                                                     |

| 2.4                                                                         | Sample code for the Smith-Waterman algorithm in the ADP language,                                                                                                                                                                                                                                                                                                                                     |                                                                        |

|                                                                             | which includes a grammar and an evaluation algebra. The code is                                                                                                                                                                                                                                                                                                                                       |                                                                        |

|                                                                             | taken from [53] and scores a match with $+1$ and a mismatch or a gap with $-1$ .                                                                                                                                                                                                                                                                                                                      | 20                                                                     |

|                                                                             | with -1                                                                                                                                                                                                                                                                                                                                                                                               | 38                                                                     |

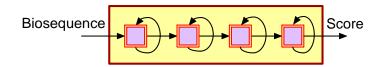

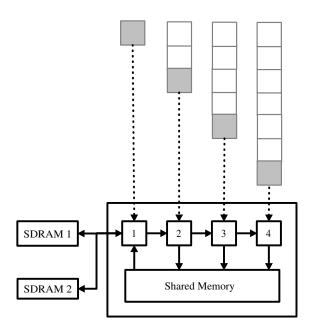

| 3.1                                                                         | A linear, four-processing-element systolic array. In this example pipeline                                                                                                                                                                                                                                                                                                                            |                                                                        |

|                                                                             | based parallelism occurs and, for long sequences, a speedup of four over                                                                                                                                                                                                                                                                                                                              |                                                                        |

| 2.2                                                                         | based parallelism occurs and, for long sequences, a speedup of four over<br>a single processor is possible                                                                                                                                                                                                                                                                                            | 44                                                                     |

| 3.2                                                                         | based parallelism occurs and, for long sequences, a speedup of four over<br>a single processor is possible                                                                                                                                                                                                                                                                                            |                                                                        |

|                                                                             | based parallelism occurs and, for long sequences, a speedup of four over<br>a single processor is possible                                                                                                                                                                                                                                                                                            | 44<br>51                                                               |

| 3.2<br>3.3                                                                  | <ul> <li>based parallelism occurs and, for long sequences, a speedup of four over</li> <li>a single processor is possible.</li> <li>Every systolic array can be described by a system of uniform recurrence</li> <li>equations.</li> <li>(a) Affine dependencies result in data broadcasts. (b) We can derive</li> </ul>                                                                              |                                                                        |

|                                                                             | based parallelism occurs and, for long sequences, a speedup of four over<br>a single processor is possible                                                                                                                                                                                                                                                                                            | 51                                                                     |

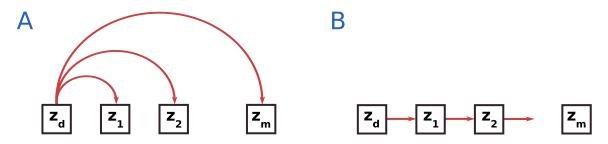

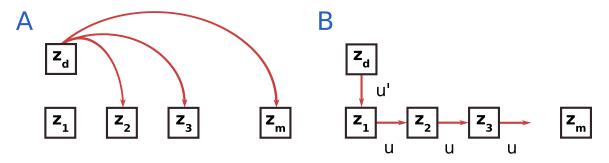

| 3.3                                                                         | <ul> <li>based parallelism occurs and, for long sequences, a speedup of four over</li> <li>a single processor is possible.</li> <li>Every systolic array can be described by a system of uniform recurrence</li> <li>equations.</li> <li>(a) Affine dependencies result in data broadcasts.</li> <li>(b) We can derive</li> <li>an equivalent uniform recurrence by pipelining broadcasts.</li> </ul> | 51<br>59                                                               |

| 3.3<br>3.4                                                                  | based parallelism occurs and, for long sequences, a speedup of four over<br>a single processor is possible                                                                                                                                                                                                                                                                                            | 51<br>59<br>60                                                         |

| 3.3<br>3.4                                                                  | based parallelism occurs and, for long sequences, a speedup of four over<br>a single processor is possible                                                                                                                                                                                                                                                                                            | 51<br>59                                                               |

| 3.3<br>3.4                                                                  | based parallelism occurs and, for long sequences, a speedup of four over<br>a single processor is possible                                                                                                                                                                                                                                                                                            | 51<br>59<br>60                                                         |

| <ul><li>3.3</li><li>3.4</li><li>3.5</li><li>4.1</li></ul>                   | based parallelism occurs and, for long sequences, a speedup of four over<br>a single processor is possible                                                                                                                                                                                                                                                                                            | 51<br>59<br>60                                                         |

| 3.3<br>3.4<br>3.5                                                           | based parallelism occurs and, for long sequences, a speedup of four over<br>a single processor is possible                                                                                                                                                                                                                                                                                            | <ul> <li>51</li> <li>59</li> <li>60</li> <li>62</li> <li>65</li> </ul> |

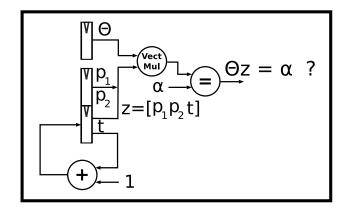

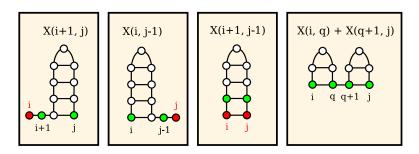

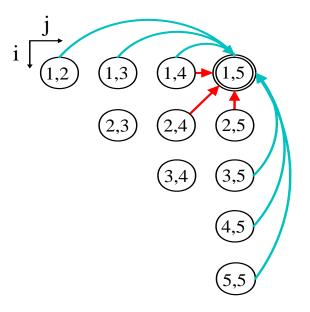

| <ul> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>4.1</li> <li>4.2</li> </ul> | based parallelism occurs and, for long sequences, a speedup of four over<br>a single processor is possible                                                                                                                                                                                                                                                                                            | 51<br>59<br>60<br>62                                                   |

| <ul><li>3.3</li><li>3.4</li><li>3.5</li><li>4.1</li></ul>                   | based parallelism occurs and, for long sequences, a speedup of four over<br>a single processor is possible                                                                                                                                                                                                                                                                                            | <ul> <li>51</li> <li>59</li> <li>60</li> <li>62</li> <li>65</li> </ul> |

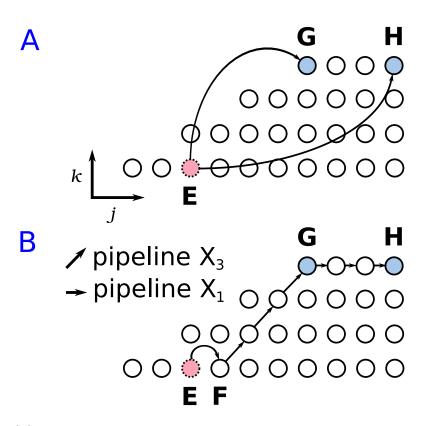

| <ul><li>4.4</li><li>4.5</li><li>4.6</li></ul> | (a) Two affine dependencies $f_3 : \mathbf{G} \leftarrow \mathbf{E}$ and $f_1 : \mathbf{H} \leftarrow \mathbf{E}$ are to be<br>pipelined. (b) Simple pipeline $X_3$ for dependency $f_3$ transfers $\mathbf{E}$ to all<br>cells $\mathbf{F}$ through $\mathbf{G}$ that require it using uniform transfers. Multistage<br>pipeline $X_1$ for dependency $f_1$ transfers $\mathbf{E}$ to all cells $\mathbf{G}$ through $\mathbf{H}$ and<br>is initialized by $X_3$                                                                                                                                                                                                 | 70<br>73<br>75 |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

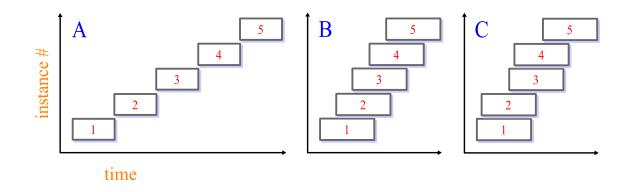

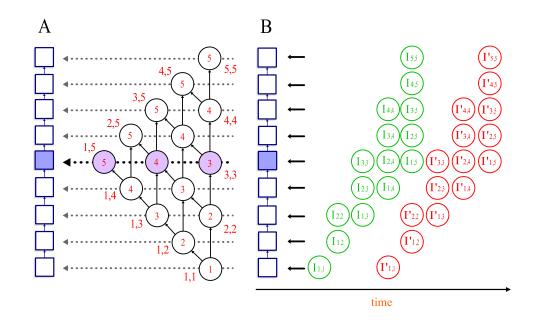

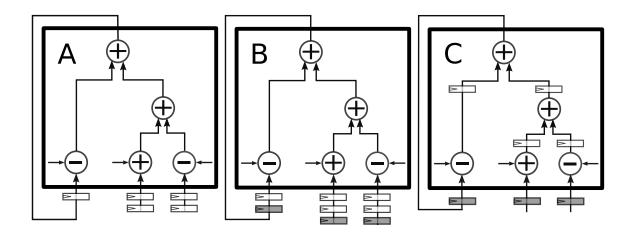

| 5.1                                           | (a) A latency-optimal array executes five input instances in sequence<br>and has an execution time of $5\mathcal{L}_{opt}$ clock cycles. (b) The array op-<br>timized for throughput pipelines a new input every $\frac{1}{3}\mathcal{L}$ clock cycles.<br>(c) When the array is not fully efficient (here 50%), we simultaneously<br>pipeline two input instances every $\frac{2}{3}\mathcal{L}$ clock cycles. The total execu-<br>tion time for arrays <b>b</b> and <b>c</b> are $\frac{7}{3}\mathcal{L}$ clocks. Though the throughput-<br>optimized arrays have higher latency, they have an overall lower exe-<br>cution time than the latency-optimal array | 86             |

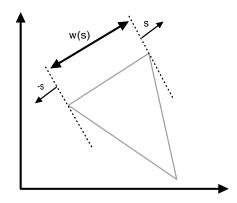

| 5.3                                           | and we are guaranteed that there will be no PE contention. $\ldots$ . Width of a convex body along the direction $\hat{s}$ . The number of domain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 88             |

| 0.0                                           | points along the unit vector $\hat{\mathbf{s}}$ is $1 + w(\hat{\mathbf{s}})$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 94             |

| 5.4                                           | <ul> <li>(a) The unpipelined PE has three operations in its critical path. (b)</li> <li>When the schedule is relaxed, new delay registers are generated on dependency links, which are moved by the circuit retimer as shown in</li> <li>(c) to reduce the length of the critical path to one operation</li> </ul>                                                                                                                                                                                                                                                                                                                                                | 100            |

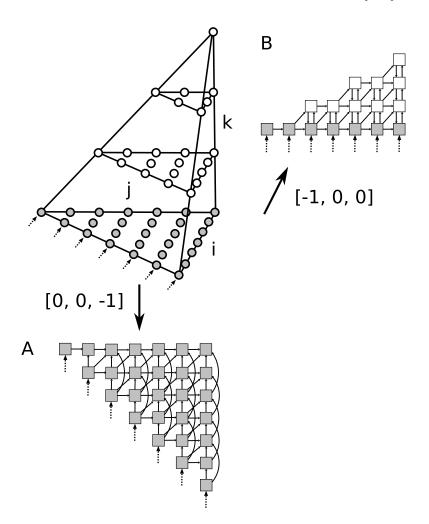

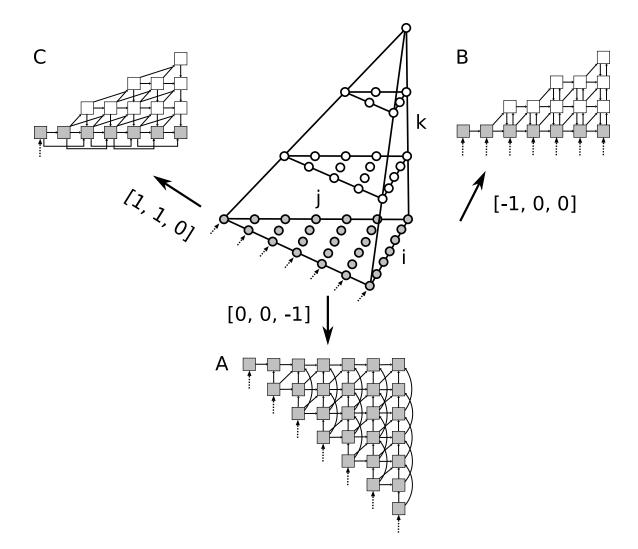

| 5.5                                           | (a) Array FS-A projects the Nussinov computation domain along direction [0, 0, -1]. (b) Projecting along direction [-1, 0, 0] yields the FS-B array. (c) Projecting along the diagonal direction [1, 1, 0] yields the FS-C array. The RNA sequence is fed into PEs indicated by dashed                                                                                                                                                                                                                                                                                                                                                                            | _ 0 0          |

| 56                                            | arrows                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 104            |

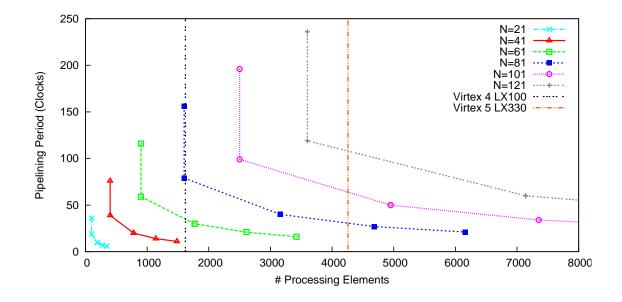

| 5.6                                           | required for arrays A-E from Table 5.2 for various values of $N$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 106            |

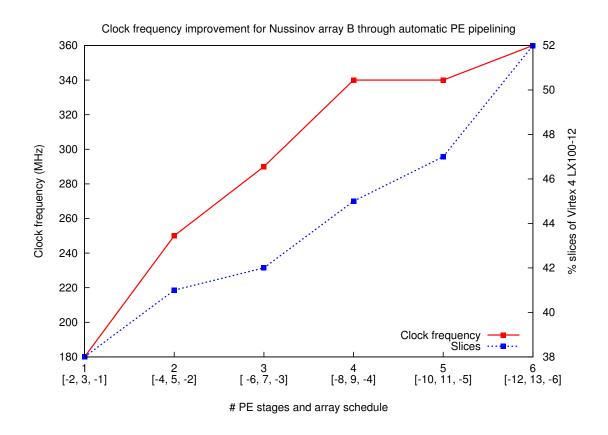

| 5.7                                           | Improvement of array clock frequency as a function of pipelined stages<br>in a Nussinov PE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 107            |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                |

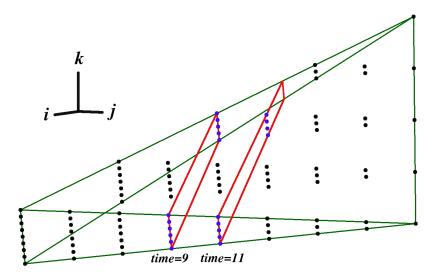

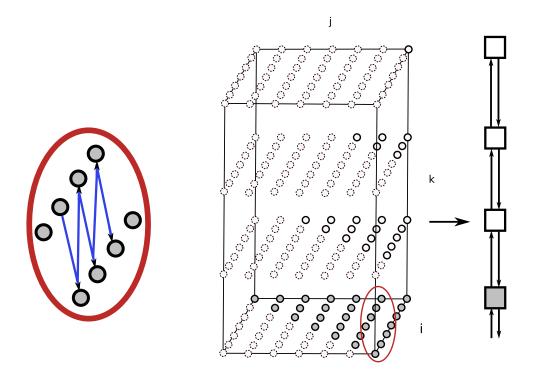

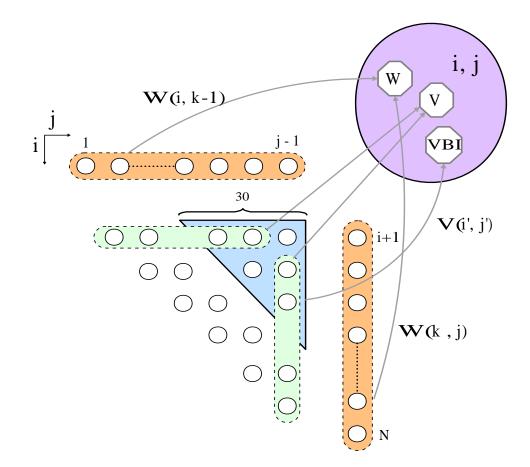

| 6.1 | The 1-D array for the transformed Nussinov recurrence is generated<br>by placing a linear array of PEs along the $k$ axis. Computation points<br>outside the original Nussinov domain are shown as dashed circles. Each<br>PE in the array sequentially executes a rectangular plane of points as                                                                                                                  |     |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | shown in the inset.                                                                                                                                                                                                                                                                                                                                                                                                | 114 |

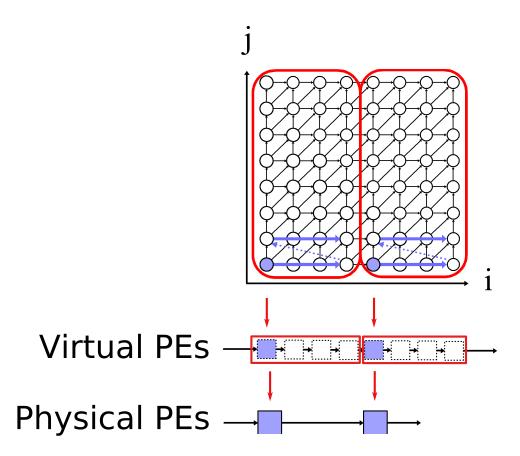

| 6.2 | A 2-D recurrence domain that is computed by a linear array. The figure illustrates how the domain is projected onto virtual PEs and then partitioned onto physical PEs. array.                                                                                                                                                                                                                                     | 115 |

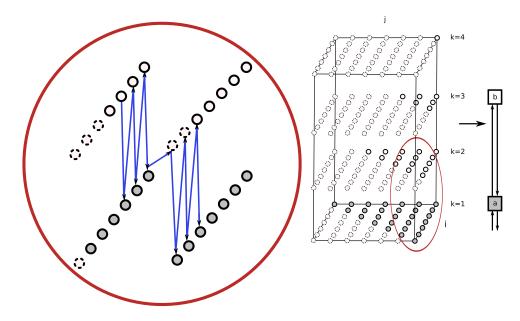

| 6.3 | The 1-D partitioned array for the transformed Nussinov recurrence<br>with $W_k = 2$ . Each PE sequentially computes two planes of points                                                                                                                                                                                                                                                                           |     |

| 6.4 | according to the schedule illustrated in the inset                                                                                                                                                                                                                                                                                                                                                                 | 119 |

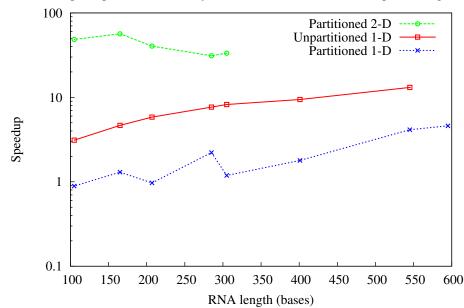

|     | speedups.                                                                                                                                                                                                                                                                                                                                                                                                          | 124 |

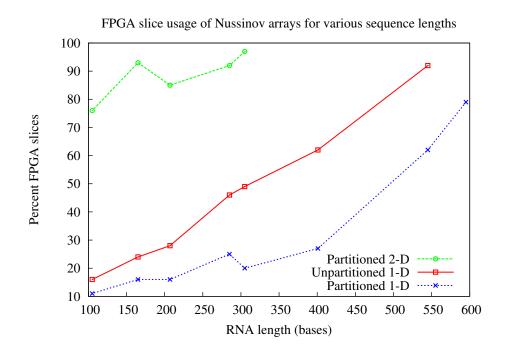

| 6.5 | Percent of the target FPGA slices used by instantiations of three array<br>types for various sequence lengths. Depending on the requirements, a                                                                                                                                                                                                                                                                    |     |

|     | designer can select the most suitable array type                                                                                                                                                                                                                                                                                                                                                                   | 125 |

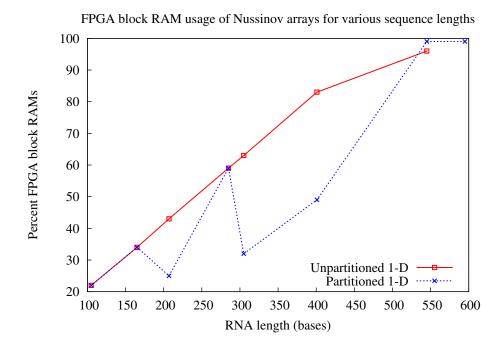

| 6.6 | Percent of the target FPGA block RAMs used by instantiations of<br>two array types. The partitioned 2-D array does not use block RAM                                                                                                                                                                                                                                                                               |     |

|     | memories.                                                                                                                                                                                                                                                                                                                                                                                                          | 125 |

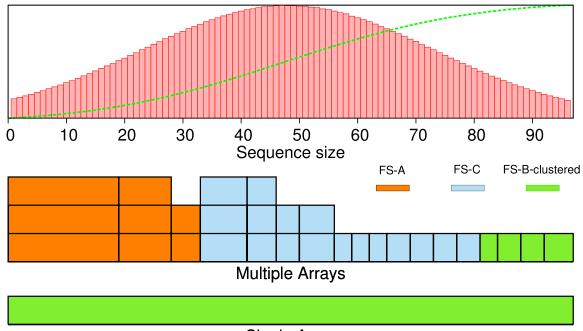

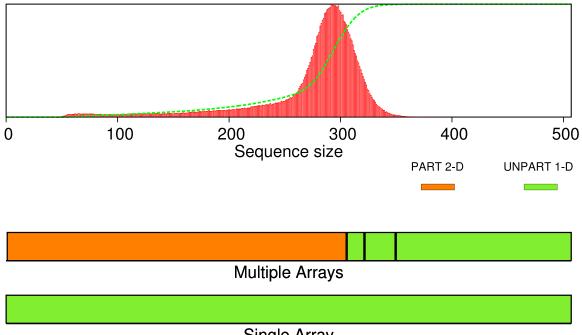

| 7.1 | Optimal selection of Nussinov arrays to fold synthetic sequences with<br>normally distributed lengths. Top: histogram and cumulative fre-<br>quency of sequence lengths. Middle: design with reconfigurations pro-<br>duced by our algorithm. Bottom: best single array supporting all input<br>lengths (up to 97 bases). Size of each array instantiation is given by<br>length of longest sequence it processes. | 136 |

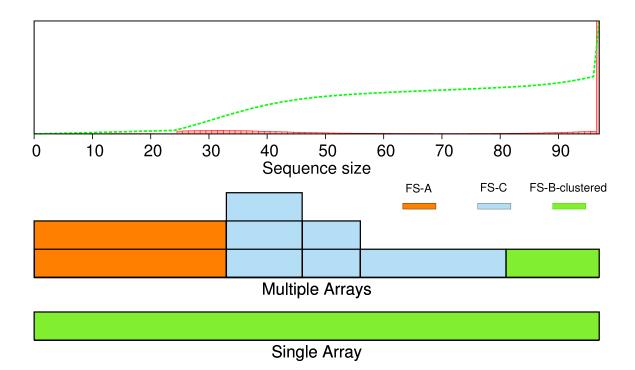

| 7.2 | Optimal selection of Nussinov arrays to fold pyrosequencing reads. Es-<br>timated speedup of the reconfigured solution over the single-array ap-<br>proach was 51%; direct measurement yielded 48%                                                                                                                                                                                                                 | 139 |

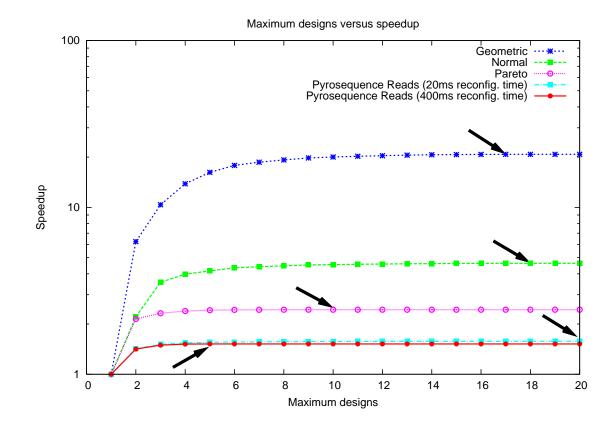

| 7.3 | Speedup of a reconfigured solution as a function of the maximum num-<br>ber of instantiations allowed. We may choose to limit the number of<br>instantiations to the knee of the curve in order to reduce synthesis<br>time. The y axis is shown in log scale.                                                                                                                                                     | 140 |

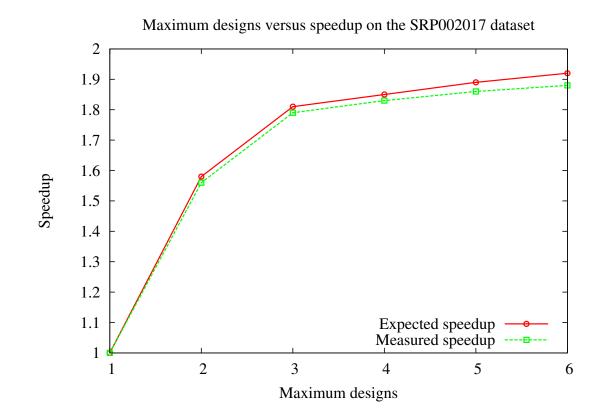

| 7.4 | Reconfiguring the FPGA using up to six Nussinov array instantiations, we are able to achieve a speedup between 56 and 88% over a single array                                                                                                                                                                                                                                                                      |     |

| 7.5 | when folding the SRP002017 dataset                                                                                                                                                                                                                                                                                                                                                                                 | 142 |

|     | optimal solution. Our algorithm suggests the use of three unpartitioned<br>1-D arrays, and a single partitioned 2-D array                                                                                                                                                                                                                                                                                          | 143 |

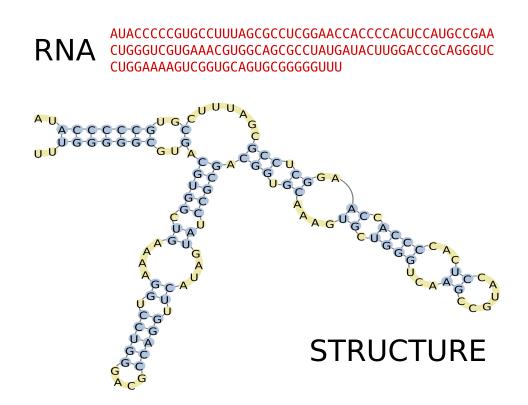

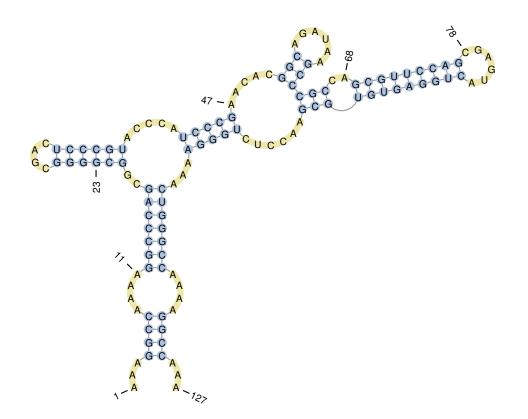

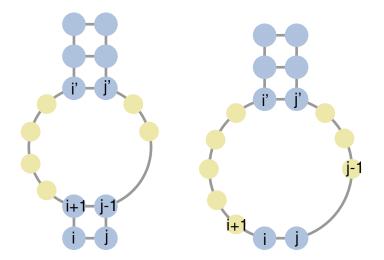

| 8.1 | An example of an RNA folded into a secondary structure with free                     |     |

|-----|--------------------------------------------------------------------------------------|-----|

|     | energy -53.90 kcal/mol. Types of structural features modeled by the                  |     |

|     | Zuker folding algorithm include: dangling ends $(1)$ , internal loop $(11)$ ,        |     |

|     | stack (23), multi-loop (47), bulge (68) and hairpin loop (78). $\ldots$              | 148 |

| 8.2 | Long-range dependencies for the cell $(i, j)$                                        | 149 |

| 8.3 | Difference in internal loop energy as the exterior base pair changes                 |     |

|     | from $(i+1, j-1)$ to $(i, j)$ . Using Equation 8.8, we see that the energy           |     |

|     | for the second loop is $ebi(i+1, j-1, i', j') - ebistacking(S_{i+1}, S_{j-1}) +$     |     |

|     | $ebistacking(S_i, S_j) - ebisize(l-2) + ebisize(l)$ . Here $l = i' - i + j - j' - 4$ |     |

|     | is the loop size.                                                                    | 153 |

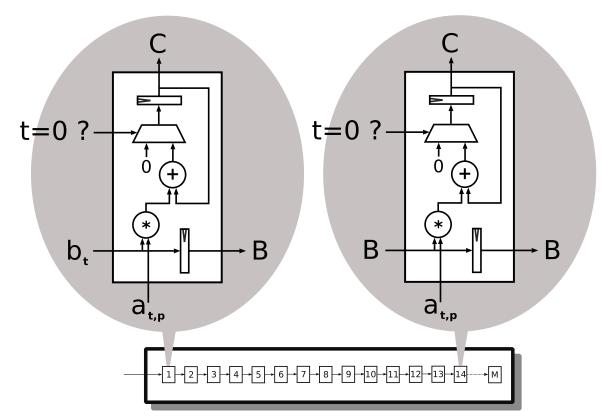

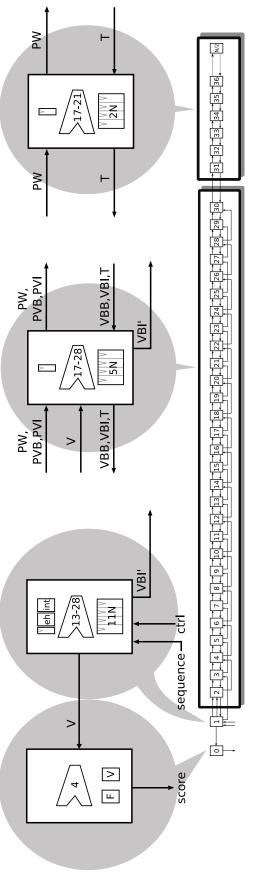

| 8.4 | Overview of the 1-D Zuker array, which uses four main PE types.                      |     |

|     | Equation numbers (from the previous section) computed by a PE are                    |     |

|     | shown in the ALU block; energy functions stored in block RAMs and                    |     |

|     | registers are shown at the top of each PE; and the growth of delay                   |     |

|     | registers as a function of RNA length is shown in the bottom block.                  | 161 |

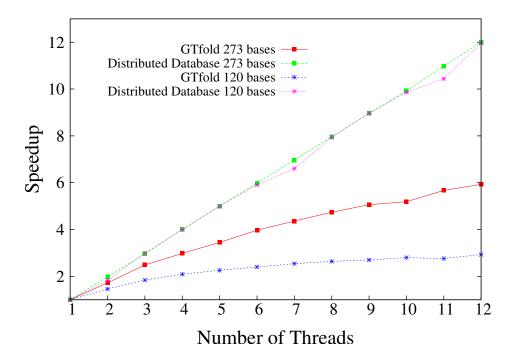

| 8.5 | Speedup of GTfold and a split database approach on a twelve-core                     |     |

|     | workstation.                                                                         | 168 |

| 8.6 | An FPGA array by Dou et al. [39] to accelerate Zuker.                                | 170 |

| 0.0 |                                                                                      | 110 |

| 9.1 | (a) A finite-state automata representation of the Smith-Waterman dy-                 |     |

|     | namic programming recurrence may be entered through a visual pro-                    |     |

|     | gramming environment. (b) Future work describing a compiler for                      |     |

|     | automated synthesis of dynamic programming accelerators.                             | 180 |

### Chapter 1

### Introduction

Dynamic programming (DP) is a computational technique based on the principle of optimality [15], which states that the optimal solution to a subproblem is part of the optimal solution to a larger problem. DP has been used to efficiently solve many combinatorial optimization problems in polynomial space and time. This technique has become widely used in fields such as control theory, operations research, finance, computer vision, speech recognition, and computational biology.

Our domain of interest is computational biology, where DP is widely used to process biosequence information. The recent arrival of high-throughput *next-generation* sequencing machines [134] allows researchers to generate millions of short sequence reads in parallel at low cost. Next-generation sequencers have enabled researchers [106] to conduct large-scale studies to detect mutations in genomes that determine phenotypes and predict risk factors of an individual, detect antibiotic resistant pathogens [70] and identify their integration sites in a host genome [159], and discover novel noncoding RNAs [85]. Another major initiative aims to study the complex microbial community that inhabit the human body [150] to understand how these organisms may regulate the intake of nutrients by individuals (and hence their susceptibility to malnourishment and obesity), drug metabolism, and immune response, and how they can even cause behavioral and psychiatric disorders.

Fast computational analyses will play a critical, and we argue, a central role, in enabling researchers realize this vision. In this dissertation we explore novel compute architectures, high-level abstractions and efficient parallelization strategies to accelerate DP algorithms used for bioinformatics analyses by one to two orders of magnitude.

### 1.1 Dynamic Programming in Computational Biology

The sequencing of the human genome has ushered in an era where computational methods play a central role in understanding the molecular processes sustaining life. The DP technique has seen use in computational biology since the early 1970s for pairwise sequence comparison, multiple alignment and secondary structure prediction [131]. In Fall 2010, a search for the phrase "dynamic programming" in the journal of *Bioinformatics*, *BMC Bioinformatics*, and *IEEE/ACM Transactions on Computational Biology and Bioinformatics* returned over 1400 articles.

Table 1.1 lists DP algorithms from the computational biology literature. It includes 25 algorithms classified under eight categories. Alignment using probabilistic [43] and non-probabilistic [57] models is most popular and has been applied to numerous biological problems. Hidden Markov models [73] have been applied to motif identification [43] and gene prediction [24]. Parsing of hidden Markov models can be done efficiently using DP. Stochastic Context-Free Grammars [129] offer a richer framework to fold RNA and protein sequences to determine their most likely secondary structure. Conditional Random Fields [92] are a new modeling technique introduced within the last several years and look set to produce more accurate results on a number of these biological problems. Most of the algorithms listed in the table represent a family of solutions that have subtle but important variations depending on the biological problem being solved.

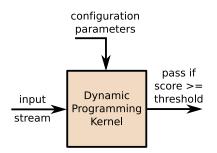

Figure 1.1: A *filter* computes the score of inputs using a DP kernel and discards those that do not cross a threshold. As a result, finding the score of the optimal solution using DP is more important than the state path that leads to the solution.

Table 1.1: A compilation of dynamic programming algorithms from computational biology. A detailed description of these algorithms, including the time and space growth functions, are in Appendix A. Legend for Accelerators: F - FPGA, G - GPU, CB - IBM Cell broadband, S - SIMD extensions on a workstation, CL - Cluster of workstations

| Algorithm                                                                                                                     | Time<br>Complexity                                                                                           | Space<br>Complexity                                                           | Accelerator           | Comments                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Alignment                                                                                                                     |                                                                                                              |                                                                               |                       | ·                                                                                                                                |

| Global/Local<br>Arbitrary Gaps                                                                                                | $\begin{array}{c} O(n^2) \\ O(n^3) \end{array}$                                                              | $\begin{array}{c} O(n^2) \\ O(n^2) \end{array}$                               | F, G, CB, S, CL<br>CL | n - sequence length.                                                                                                             |

| Profile HMMs                                                                                                                  |                                                                                                              |                                                                               |                       |                                                                                                                                  |

| Full Viterbi<br>Full Forward<br>Plan7 Viterbi<br>Plan7 Forward<br>Posterior-Viterbi<br>HMM-HMM Alignment<br>MSA-HMM Alignment | $\begin{array}{c} O(nl^2) \\ O(nl^2) \\ O(nl) \\ O(nl) \\ O(nl) \\ O(nl) \\ O(l^2) \\ O(nl) \end{array}$     | $O(nl) \\ O(nl) \\ O(nl) \\ O(nl) \\ O(nl) \\ O(nl) \\ O(l^2) \\ O(l)$        | F, G, CB, S, CL       | n - sequence length.<br>l - model length.                                                                                        |

| Gene Prediction                                                                                                               |                                                                                                              |                                                                               |                       |                                                                                                                                  |

| GHMM Viterbi<br>GHMM Forward<br>GPHMM Viterbi<br>GPHMM Forward<br>GeneWise                                                    | $\begin{array}{c} O(n^{3}l^{2}) \\ O(n^{3}l^{2}) \\ O(mnl^{2}d^{4}) \\ O(mnl^{2}d^{4}) \\ O(mn) \end{array}$ | O(nl)<br>O(nl)<br>O(mnl)<br>O(mnl)<br>O(mn)                                   |                       | <ul> <li>m,n - sequence length.</li> <li>l - model length.</li> <li>d - maximum length of observations in each state.</li> </ul> |

| Secondary Structure                                                                                                           |                                                                                                              |                                                                               |                       |                                                                                                                                  |

| Nussinov<br>Zuker<br>Zuker and Lyngsø<br>PKNOTS<br>Rnall                                                                      | $O(n^3) \\ O(n^4) \\ O(n^3) \\ O(n^6) \\ O(w^3n)$                                                            | $\begin{array}{c} O(n^2) \\ O(n^2) \\ O(n^2) \\ O(n^4) \\ O(w^3) \end{array}$ | F, CL<br>CL<br>CL     | n - sequence length.<br>w - window length.                                                                                       |

| Simultaneous Sequence                                                                                                         | e and Structu                                                                                                | ral Alignment                                                                 |                       |                                                                                                                                  |

| Sankoff<br>FOLDALIGN                                                                                                          | $O(n^6) \\ O(n^4)$                                                                                           | $\begin{array}{c} O(n^4) \\ O(n^4) \end{array}$                               |                       | <i>n</i> - sequence length.                                                                                                      |

| Stochastic Context-Fr                                                                                                         |                                                                                                              |                                                                               |                       |                                                                                                                                  |

| Inside/Outside<br>CYK<br>Inside for Pair SCFGs                                                                                | $O(l^2n^3) \\ O(l^2n^3) \\ O(n^3m^3)$                                                                        | $\begin{array}{c} O(ln^2)\\ O(ln^2)\\ O(n^2m^2) \end{array}$                  | F<br>F                | m,n - sequence length.<br>l - number of states in model.                                                                         |

| Conditional Random                                                                                                            | Fields                                                                                                       |                                                                               |                       |                                                                                                                                  |

| CRF-Forward<br>CRF-Viterbi                                                                                                    | $O(nl^2) \\ O(nl^2)$                                                                                         | $O(nl) \ O(nl)$                                                               |                       | n - sequence length.<br>l - number of states in model.                                                                           |

| Haplotyping Problem                                                                                                           |                                                                                                              |                                                                               |                       |                                                                                                                                  |

| MSR                                                                                                                           | $O(mn^2)$                                                                                                    | O(n)                                                                          |                       | m - number of fragments.<br>n - number of SNP sites.                                                                             |

DP kernels are often employed as *filters*, as illustrated in Figure 1.1. The filter may be configured using one or more *query* parameters, such as a sequence or a probabilistic model. A *database* of discrete inputs, such as sequences, are then streamed through the kernel. The DP computation is applied to each input, and a score is computed; those inputs that score above a threshold are reported for inspection by the user. Filters often discard a majority of inputs in the database stream, which are too low-scoring to cross the threshold of interest. As a consequence, it is more important to be able to quickly compute the score of an optimal solution rather than the sequence of decisions that lead to the optimal solution.

Some filters have no configuration parameters. For example, to identify novel microR-NAs, one simply folds a stream of input sequences. In contrast, pairwise alignment configures the filter with a query sequence and then streams a database of sequences through. Furthermore, the filter may be repeatedly reconfigured with a new query, and the computation repeated on the entire database. Here, the goal is to identify query-database pairs that score above a threshold and may be of interest to the user. In this work, we assume that the query set is always large enough so that the time and space complexity of filters depend on the size of both the query and the database. We will henceforth refer to all filters as *search* applications.

Search applications are useful for quickly identifying a small subset of sequences that can then be studied using time-consuming, more manual analyses. For example, we used NCBI BLAST [7] to compare a virus sequence against the NR nucleotide database containing 14,332,765 sequences. The search completed in tens of seconds and returned under 1934 matching sequences (< 0.14% of the database) sorted by the statistical significance of each match.

One way of accelerating search applications is to use heuristics to approximate the DP computation. Examples include NCBI BLAST [7] and HMMERHEAD [120] to accelerate pairwise sequence alignment and motif finding respectively. These applications use a variety of computationally inexpensive kernels to discard a majority of inputs before applying expensive DP. The design of heuristics is beyond the scope of this work—we look to accelerate the full DP computation. Nevertheless, applications that use heuristics often employ a filtering pipeline consisting of progressively

more computationally expensive DP kernels, which account for a significant fraction of program execution time.

### 1.2 A Bottleneck in Computational Biology Analysis

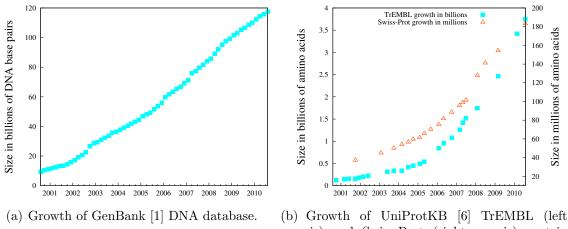

y axis) and Swiss-Prot (right y axis) protein databases.

Figure 1.2: The growth of biosequence databases is straining computational analysis pipelines.

An explosion of sequence information over the last decades has led to a computational bottleneck in the DP-based applications analyzing them. DNA and protein databases are growing in size as new organisms and environmental samples are sequenced. Figure 1.2 shows the sustained growth of popular DNA and protein databases over the last decade. Moreover, as listed in Table 1.1, the DP algorithms that operate on this data are compute-bound and frequently run in time quadratic or worse in the input size.

Biologists have relied on advances in integrated circuit technology to keep pace with the increasing computational demands of their work. Over the past four decades the number of transistors per unit area has doubled every two years, a phenomenon referred to as Moore's Law. Microprocessor vendors have in turn been able to achieve a twofold increase in CPU performance every 18 months (we will henceforth refer to the doubling of CPU performance as Moore's Law). Underwood [151] notes that between 1998 and 2003 clock speed improvement yielded a  $12 \times$  increase in CPU performance compared to only a  $4 \times$  improvement due to architectural enhancements. Clock speed increase has been the primary contributor to an essentially "free" performance boost for computational biology applications.