#### WASHINGTON UNIVERSITY IN ST. LOUIS

McKelvey School of Engineering

Department of Computer Science & Engineering

Dissertation Examination Committee:

Roger Chamberlain, Chair

Jeremy Buhler

Ron Cytron

Chris Gill

Martin Herbordt

Improving and Modeling Heterogeneous Streaming Computation by Clayton Faber

A dissertation presented to the McKelvey School of Engineering of Washington University in partial fulfillment of the requirements for the degree of Doctor of Philosophy

> May 2024 St. Louis, Missouri

## Table of Contents

| List of | Figures                                              | iv              |  |  |  |

|---------|------------------------------------------------------|-----------------|--|--|--|

| List of | Tables                                               | vi              |  |  |  |

| Ackno   | wledgments                                           | vii             |  |  |  |

| Abstra  | <u>uct</u>                                           | iii             |  |  |  |

| Chapte  | er 1: Introduction                                   | 1               |  |  |  |

| 1.1     | Contributions                                        | 4               |  |  |  |

| 1.2     | Outline                                              | 6               |  |  |  |

| Chapte  | er 2: Background and Related Work                    | 7               |  |  |  |

| 2.1     | Related Work                                         | 9               |  |  |  |

| Chapte  | er 3: Streaming Data Tasks for Heterogeneous Compute | 13              |  |  |  |

| 3.1     | 0 1                                                  | 13              |  |  |  |

| 3.2     |                                                      | 14              |  |  |  |

| 3.3     | •                                                    | 16              |  |  |  |

| 3.4     |                                                      | 18              |  |  |  |

| 3.5     |                                                      | $2\overline{1}$ |  |  |  |

| 3.6     | 1 0 1                                                | 22              |  |  |  |

| 3.7     | Conclusion                                           |                 |  |  |  |

| Chapte  | er 4: Queueing Models for Streaming Data Computation | 26              |  |  |  |

| 4.1     | • •                                                  | 26              |  |  |  |

| 4.2     |                                                      | 27              |  |  |  |

|         | 11                                                   | 27              |  |  |  |

|         | 4.2.2 ML                                             | 28              |  |  |  |

| 4.3     | Queueing Theory Model                                | 30              |  |  |  |

|         |                                                      | 31              |  |  |  |

| 4.4     |                                                      | 35              |  |  |  |

|         |                                                      | 35              |  |  |  |

|         | · · · · · · · · · · · · · · · · · · ·                | 36              |  |  |  |

|         | 4.4.3 Network Connection                             | 36              |  |  |  |

|        | 4.4.4 Empirical Measurements                     | 37   |

|--------|--------------------------------------------------|------|

| 4.5    | Performance Results                              | 38   |

|        | 4.5.1 BLAST                                      | 38   |

|        | 4.5.2 ML                                         | 39   |

| 4.6    | Utilizing the Model for Implementation Decisions | 40   |

|        | 4.6.1 Alternative Topology                       | 40   |

|        | 4.6.2 Cost Modeling                              | 41   |

| 4.7    | Conclusion                                       | 42   |

| Chapte | er 5: Network Calculus for Streaming Algorithms  | . 44 |

| 5.1    | Introduction                                     |      |

| 5.2    | Introduction to Network Calculus                 |      |

| 5.3    | Network Calculus Modeling                        | 46   |

| 5.4    | Modeling and Simulation of BLAST                 | 49   |

| 5.5    | Bump in the Wire Streaming Algorithms            | 52   |

| Chapte | er 6: Conclusions and Future Work                | . 58 |

| 6.1    | Conclusions                                      |      |

| 6.2    | Future Work                                      | 59   |

| Refere | nces                                             | . 61 |

# List of Figures

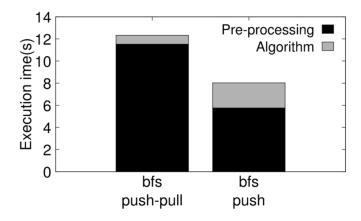

| Figure 1.1: | Example of the trade-off between pre-processing and algorithm execution time for BFS on the Twitter graph [70]                                                                           | 2  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

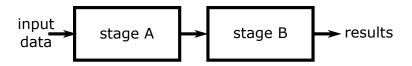

| Figure 2.1: | Example streaming application                                                                                                                                                            | 7  |

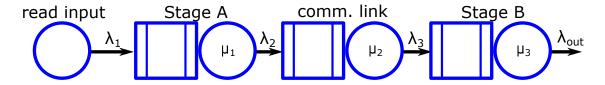

| Figure 2.2: | Example streaming application flow model                                                                                                                                                 | 8  |

| Figure 2.3: | Example streaming application queueing network model                                                                                                                                     | 8  |

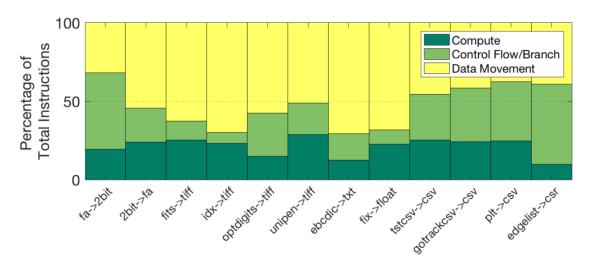

| Figure 3.1: | Data Integration Benchmark Suite application classification [22]                                                                                                                         | 14 |

| Figure 3.2: | Instruction Mix of DIBS Applications on x86 [22]                                                                                                                                         | 15 |

| Figure 3.3: | Illustration of the MWI and SWI OpenCL programming models                                                                                                                                | 17 |

| Figure 3.4: | Speedup of MWI over SWI implementations. Applications are $2k \times 2k$ and $4k \times 4k$ matrix-matrix multiply plus data integration applications ebcdic_txt and fix_float from DIBS | 18 |

| Figure 3.5: | Bandwidth comparison numbers for selected DIBS benchmarks running on multicore CPU and HARP FPGA machines                                                                                | 20 |

| Figure 3.6: | Data size vs. execution time on HARP for versions of the fix->float kernel                                                                                                               | 22 |

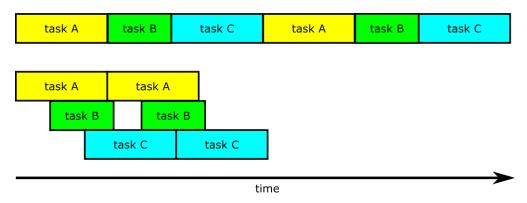

| Figure 3.7: | Illustration of dataflow execution with 3 tasks. The top diagram illustrates a sequential execution timeline, while the bottom diagram illustrates a pipelined execution timeline        | 24 |

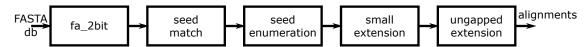

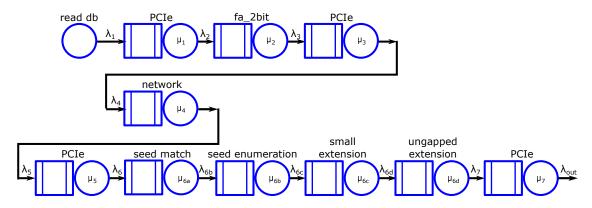

| Figure 4.1: | BLAST application                                                                                                                                                                        | 27 |

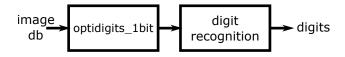

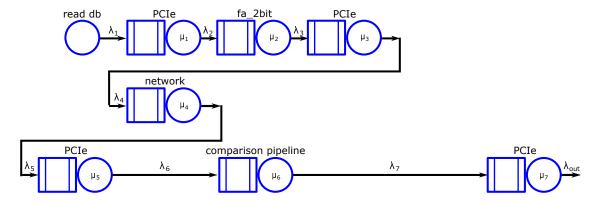

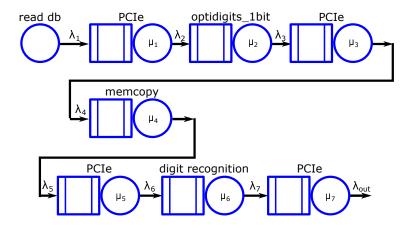

| Figure 4.2: | ML application – handwriting recognition                                                                                                                                                 | 29 |

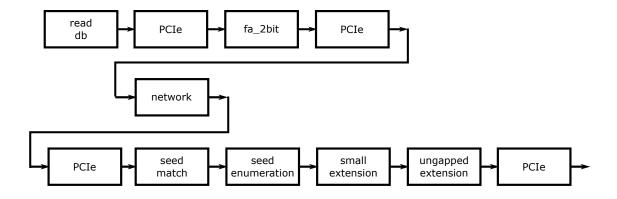

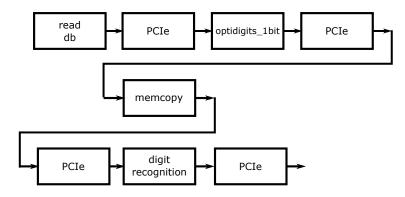

| Figure 4.3:  | Flow graph for BLAST application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 32 |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

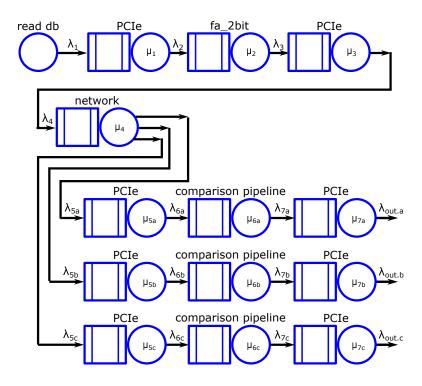

| Figure 4.4:  | Queueing network for BLAST application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 32 |

| Figure 4.5:  | Modified queueing network for BLAST application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 33 |

| Figure 4.6:  | Flow graph for ML application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 33 |

| Figure 4.7:  | Queueing network for ML application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 34 |

| Figure 4.8:  | Queueing network for multiple BLAST comparison pipelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 41 |

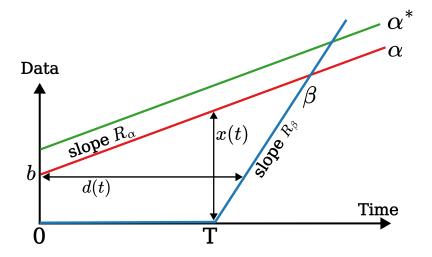

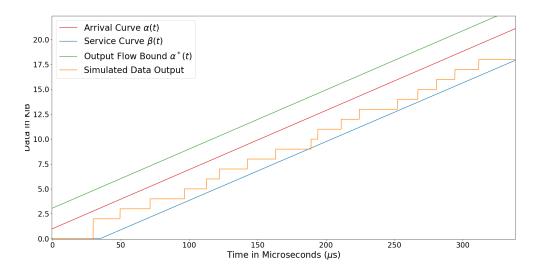

| Figure 5.1:  | Plot of a Leaky Bucket Arrival Curve, $\alpha$ , and a Rate-Latency Service Curve, $\beta$ , showing the relation of the Backlog, $x(t)$ , Virtual Delay, $d(t)$ , and Output Flow, $\alpha^*$ , bounds. Adapted from [61]                                                                                                                                                                                                                                                                                                                 | 47 |

| Figure 5.2:  | BLAST queueing model (from Figure 4.5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 50 |

| Figure 5.3:  | Data flow diagram with accompanying node table with names and throughput for BLAST. Nodes represent computations or communications, and the job ratio is shown below each node. Node D decomposes large data blocks from the FPGA for delivery over the network, and Node E composes even larger data blocks for delivery to the GPU. Average, Maximum, and Minimum throughput for each node are also listed, except for Data Source as we assume the source to have infinite throughput (a job will be queued immediately when arriving). | 50 |

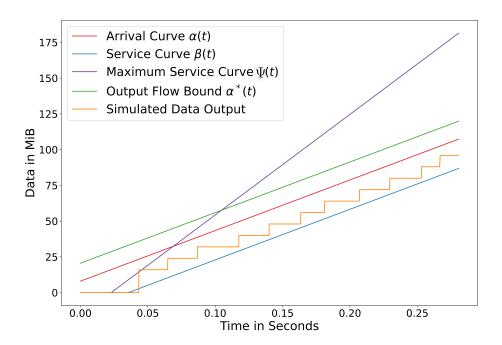

| Figure 5.4:  | Network calculus model results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 51 |

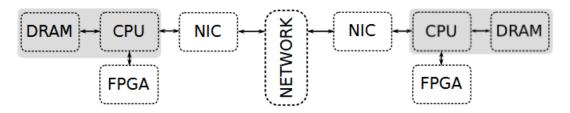

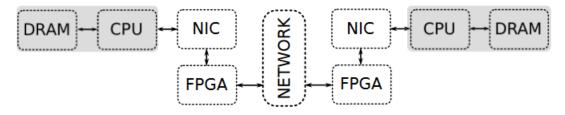

| Figure 5.5:  | Traditional FPGA accelerator [59]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 52 |

| Figure 5.6:  | Bump in the wire FPGA accelerator [59]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 53 |

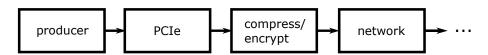

| Figure 5.7:  | Example flow graph for FPGA accelerated compression/encryption using a traditional FPGA interconnection                                                                                                                                                                                                                                                                                                                                                                                                                                    | 53 |

| Figure 5.8:  | Example flow graph for FPGA accelerated compression/encryption using a bump in the wire configuration                                                                                                                                                                                                                                                                                                                                                                                                                                      | 54 |

| Figure 5.9:  | Actual flow graph for FPGA accelerated compression/encryption using the bump in the wire configuration                                                                                                                                                                                                                                                                                                                                                                                                                                     | 55 |

| Figure 5.10: | Network calculus model for our bump in the wire application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 56 |

## List of Tables

| Table 3.1: | Measured throughputs for MWI and SWI implementations                                                                                                     | 18 |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 4.1: | AWS EC2 Instances used for BLAST and ORNL and WU machines used for ML                                                                                    | 35 |

| Table 4.2: | Data Volume Gain at each Queueing Server (BLAST)                                                                                                         | 37 |

| Table 4.3: | Data Volume Gain at each Queueing Server (ML)                                                                                                            | 38 |

| Table 4.4: | Capacity (Service Rate) of each Queueing Server                                                                                                          | 39 |

| Table 4.5: | BLAST Figure 4.5 Modeled Performance                                                                                                                     | 39 |

| Table 4.6: | ML Figure 4.7 Modeled Performance                                                                                                                        | 40 |

| Table 4.7: | BLAST modeled performance utilizing a free tier CPU node                                                                                                 | 42 |

| Table 5.1: | Streaming data application throughput                                                                                                                    | 52 |

| Table 5.2: | Listing of functions and their associated throughputs. The compression                                                                                   |    |

|            | rates listed here are normalized with respect to their observed compression ratios: $2.2 \times$ Average, $1.0 \times$ Minimum, and $5.3 \times$ Maximum | 55 |

| Table 5.3: | Streaming data application throughput                                                                                                                    | 56 |

## Acknowledgments

When I started my academic career I definitely didn't expect to end up in a PhD program and now that this body of work sits before me I'm still shocked that I ended up here. There were certainly times I didn't believe that I was capable of completing undergrad studies let alone an entire PhD dissertation. I will be forever grateful for the people mentioned here for not giving up on me whether it be in the form of a mentor, a comrade, a friend, a family member, or likely some combination of these traits. The journey was arduous but I knew that I had people at my back for support, thank you, from the bottom of my heart.

To my family for their love and support: Terry Faber, Sara Faber, Libby Esile, Beamer Esile, my nieces: Ruby and Stella Esile, and, of course, all the extended Faber and Schafer clans.

To my committee and mentors that never gave up on me: Jeremy Buhler, Ron Cytron, Chris Gill, Martin Herbordt, Brad Noble, George Engel, Scott Smith, Steve Muren, and Tim York. Also an important dedication to my advisor, Roger Chamberlain, thank you for taking a chance on me from the very start of this journey.

To my friends and comrades, partners in camaraderie and crime: Mark Ostroot, Mitch McKay, Justin Deters, Kat Saurllo, Tom Plano, Kyle Singer, Anthony Cabrera, Chenfeng Zhao, Luke Hunt, Courtney Hunt, Christian Cool, Tyler Mustard, Marion Sudvarg, Steven Harris, and Steven Timcheck.

To those who are gone too soon, I hope I made you proud: Dorine Schafer, John Schafer, Francis Faber, Carol Faber, Sue Schoth, Rose Lewis and Joe Schafer, and Sandie Barrie.

This work was supported by NSF awards CNS-1527510 and CNS-1763503 and a gift from BECS Technology, Inc.

Clayton Faber

Washington University in St. Louis May 2024

#### ABSTRACT OF THE DISSERTATION

Improving and Modeling Heterogeneous Streaming Computation

by

#### Clayton Faber

Doctor of Philosophy in Computer Engineering

Washington University in St. Louis, 2024

Professor Roger Chamberlain, Chair

Data streaming algorithms are a class of problems that deal with moving data through a system while being processed. When implementing these types of algorithms a developer will spend time tuning an implementation for deployment, but if they are using heterogeneous architectures or when nodes of computation are physically separate from one another performance may be lost to unforeseen data movement complications. In this work we aim to alleviate some of these pain points through a combination of programming advice and mathematical models.

One of the pain points often unseen and underappreciated by developers is a type of data streaming task known as data integration, which are tasks that transform one data element form into another form, usually targeting some other step in the overall processing pipeline. When studying how to improve these types of tasks, we implement them across a variety of execution platforms. Of particular interest to us, we give advice on how to implement such tasks on FPGA architectures. Beyond individual data streaming tasks we then utilize mathematical modeling to understand how individual nodes of computation effect the full data flow of a streaming algorithm. Here we apply existing queuing theory models to reason about average performance of the algorithm and also make estimations on the cost of using the system. To speak on absolute bounds of the system we turn to network calculus which allows us to make estimates of latency on data throughput in the system and predictions

of queue bounds on a node for given arrival and service processes. This represents the first known application of network calculus techniques to streaming data applications.

## Chapter 1

### Introduction

In the world of computer science we often concern ourselves with the idea of algorithms to solve problems: brute force, dynamic programming, machine learning, approximation algorithms, artificial intelligence, and numerous other options. Researchers and developers alike spend a majority of their time creating, analyzing, and testing, all in hopes that their solution might be the prolific application in their field. Time and resources are spent finding an optimal strategy that accounts for both hardware and software implementations. Going further, while a single algorithm may be optimal, they are often one part of a much larger system where information produced by algorithms are utilized by other algorithms, analyzed for metadata, or even stored for later retrieval. The developers in question now have to spend the time implementing and optimizing a single algorithm for deployment but consider a larger system that has interactions with other modules. These types of systems are often considered as streaming algorithms, or streaming data applications, where data is processed in chunks sequentially and sent downstream for some other purpose and are distinctively different from algorithms that are standalone running on singleton data sets. Streaming algorithms often exist as a service, acting on requests or when a larger data set needs to be broken into chunks for individual work.

When streaming algorithms are implemented by developers they often experience additional problems that can effect performance in ways that a singleton algorithm may not consider. Often the input data exists in a separate location than the target platform where the algorithm is slated for execution, either coming from sensors in the real world or remote data stores. Taking it further, once the data arrives at a target machine it may need to be modified or transformed in some way before feeding it directly to the target. This can often take the form of changing an input format from one representation into another, or a re-arrangement of data in a table. Once the programmer gets around to tackling these problems, they may

find that with all the extra overhead their impressive mountain of an algorithm now looks like a molehill unable to reach projected performance.

For programmers one imperative is to find efficient and effective methods of both transforming the data into a correct format and delivering it to the eventual target computation node. Researchers from EPFL published an example showing that while an algorithm change might show improvement, the small amount of improvement is dwarfed by the actual time spent in the pre-processing step, which increased more than the algorithm time improved [70]. The specific example is a pair of algorithms for Breadth First Search (BFS) on a graph. Previous work [11] had shown that a push-pull approach results in a  $3\times$  improved execution time relative to the traditional push algorithm. However, due to the need for a different data layout in the push-pull algorithm, the pre-processing time increased by  $2\times$ , and since pre-processing dominates the execution time, this results in a  $1.5\times$  increase in overall execution time. This is illustrated in Figure 1.1 (from [70]).

Figure 1.1: Example of the trade-off between pre-processing and algorithm execution time for BFS on the Twitter graph [70].

These pre-processing tasks, often called *data integration* tasks, are often unreported in overall algorithm running time, but are of course necessary and vital for the computation to take place. Often when one wishes to speed up a task, such as a data pre-processing step, hardware accelerators and parallel programming become reasonable targets of investigation, and when this requires data movement from a disparate source to a computation destination the best approach often becomes even more unclear. Therefore, it becomes imperative to understand not only how to efficiently and effectively perform the required computations but also how we move data throughout the system.

Currently in computer architecture there is a focus on how data is moved throughout a system as well as computational accelerators that specialize in a class of computations. Most of this driving force comes from the slowdown in Moore's law and an end to Dennard scaling, as the physical limits of what may be possible with current transistor technology are hit. Through these innovations, domain specific languages and hardware have taken off in the last decade, giving huge performance gains if the problem maps well to these tools. Technologies like systolic architectures such as tensor cores and vector engines such as GPUs map well to specific classes of problems and can be helpful for many algorithms, however a data integration task is not always straightforward in its implementation as each task can be wildly different. Flexible architectures, such as Field Programmable Gate Array (FPGA) accelerators can potentially offer solutions that are tailor made to the task at hand.

FPGAs are a type of accelerator architecture that by their very nature are customized to the computation. Utilizing hardware description languages, higher level languages like C with a high level synthesis compiler, or both one can write a program that performs a data integration task and then actualize the hardware for a task creating a highly specialized compute platform. FPGAs can also play a role in alleviating some of the pain points of data streaming applications when data has to traverse a network, via direct network access available on some specific platforms. It is reasonable to assume that this will help mitigate bottlenecks in streaming applications associated with the movement of data across a network, however problems still arise with reasoning how these discrete processing algorithm kernels interact at a larger scale.

When considering a data streaming application at a higher level the interactions of data movement and performance using heterogeneous hardware become apparent. While devices can utilize specialized hardware for data movement, the relocation of data to discrete memory zones can impact performance to the point where if not handled properly the benefit can become dwarfed by the data movement. Understanding how to mitigate the effects of data movement can be an involved process when considering a fully working deployment where the effects of one node can interact with the performance on a node further downstream by changing data size or processing time. It is our hypothesis that tools that can be used offline and utilize measurements taken in isolation can help inform a developer how design decisions will effect the streaming data algorithm prior to implementation of the full application online.

Models that can be utilized offline can be of great benefit to any developer, helping them test and refactor designs that expend effort in actual implementation. It is through both a combination of programming guidance and mathematical modeling that one can reason about performance in a way the minimizes the effort of developers when it comes to implementing streaming data applications.

#### 1.1 Contributions

In this work we focus on streaming data applications in multiple execution environments, what their characteristics are, how to model their performance, and how to effectively implement them in heterogeneous environments. Utilizing the platform-independent utility OpenCL we are able to target both CPU, GPU, and FPGA platforms and compare performance across the platforms. Of these platforms, we are particularly interested in FPGA platforms for their performance and give general programming advice for implementors. For our streaming data applications we target data integration tasks which involve the transforming of data from either one format to another or massaging data such as rearrange or removing columns in a CSV file. These data integration tasks are usually under-appreciated in many applications and a piece of a larger system similar to stages in other streaming data applications and while one stage may be performant it is important to understand the system in aggregate.

In our efforts to improve data streaming applications we turn to queuing theory to help model the system as a series of servers sending data from one stage to another. This achieves two goals: Giving a general idea on upper-bound performance and allows us to model not only the algorithm stages but also unseen effects related to data movement in the system. The latter of these two is of particular importance when it comes to utilizing heterogeneous hardware in streaming applications due to the movement of memory between zones. This model utilizes the basic M/M/1 queuing model and can be derived from measurements taken in isolation requiring little overhead on the developers part when testing instead of implementing a fully functioning system. This model also has the added benefit of analyzing value when it comes to implementing parts of algorithms on hardware with a cost. In effect, it is an economic model as well as a performance model.

When looking into how closely the queueing model matches a predicted result with a real-world result we see that the roof-line performance does not tell the whole story. To further our understanding of these systems and in an attempt to build a more accurate model we turned to network calculus to help fill the gaps. Network calculus, although originally developed for the analysis of networking equipment, has properties that lend themselves well to performance modeling for heterogeneous streaming application. Utilizing min-plus algebra, network calculus seeks to make guarantees on service provided by individual nodes in a system. This has the property of both retaining each node's isolation but also allowing the concatenation of nodes to potentially simplify any section in the pipeline. In this work we present our adaption of network calculus to a heterogeneous streaming data application and it's evaluation when compared to both simulated and real-world results.

The specific contributions of the dissertation include the following:

- Analysis of data integration applications across platforms. Utilizing OpenCL on data integration tasks, a sub-class of streaming data applications, for deployment on multiple types of hardware (CPU, GPU, and FPGA) [22, 37].

- General programming advice for streaming data applications on FPGA hardware. We make recommendations for implementing such applications on FPGA hardware utilizing OpenCL High-Level Synthesis [37, 38].

- Development and analysis of queueing theory models for streaming computations. In an attempt to reason about the performance of data streaming applications on heterogeneous compute engines we develop a model based on queuing theory and test modeled results with real world data [36].

- Development and analysis of network calculus models for streaming computations. We also develop a model based on network calculus to help us reason more about maximum delay through the system and queue sizes between different stages of the data streaming algorithm [35].

Both the queueing models and network calculus models are tested against simulated and real world results in order to test their validity and get a sense of how closely models match the real world. The goals with these models are to require little of developers in terms of data collection and knowledge about the system intricacies.

### 1.2 Outline

The outline of the dissertation is as follows. Chapter 2 provides background and related work. Chapter 3 describes the streaming data tasks that we investigate and their implementation on a variety of hardware platforms. Chapter 4 presents the queueing theory performance models and their evaluation, and Chapter 5 introduces the network calculus performance models and their evaluation. Chapter 6 gives conclusions and future work.

### Chapter 2

## Background and Related Work

Streaming data applications have been a target of study for a considerable time, well over twenty years [90]. Examples of development platforms for the streaming paradigm include Auto-Pipe [25], Brook [17], Raftlib [15], StreamIt [92], and Streams-C [41]. In addition, each of these development platforms supports (or has been extended to support) computational accelerators, either FPGAs or GPUs.

Figure 2.1 illustrates an example streaming application with two compute nodes (labeled Stage A and Stage B). Data outbound from Stage A is delivered, as input, to Stage B by the run-time system. Common examples are applications in which the input data are not in the appropriate form or format for the computation of interest, so a pre-processing or data integration step is inserted ahead of the computation so as to enable the computation to proceed. In these examples, Stage A is the data integration and Stage B is the computation of interest. In the models presented here we make the assumption that the asymptotic complexity stays linear for all stages of the streaming application. We also make the assumption that the resources are dedicated to the current task and are not being shared with other users in the cloud or other applications. (Work that relaxes this assumption with simple sharing models for FPGAs and traditional processor cores is described by Beard [12, 13].) This paradigm readily supports the two nodes being executed on distinct execution platforms, whether they be processor cores, FPGAs, GPUs, or some other accelerator, and the data delivery might be via shared memory, PCIe bus, or the network.

Figure 2.1: Example streaming application.

When modeling the flow of data down the pipeline, it is prudent to explicitly recognize that this data movement might be the primary contributing factor to the overall performance, and as such should be included in the model. This is readily accomplished by inserting an additional node in the pipeline that represents the communication task (see Figure 2.2). By modeling each node as a queueing station (with ingest rate  $\lambda$  and service rate  $\mu$ ), the resulting queueing network is shown in Figure 2.3 [12]. Prior works by Choi et al. [29] and Gu and Wu [43] make use of similar models, however, these works are more concerned with the online scheduling of tasks whereas our focus is on a more static analysis that a programmer may use to reason about how an application could be distributed in a platform agnostic way.

Figure 2.2: Example streaming application flow model.

Figure 2.3: Example streaming application queueing network model.

While this model is useful, it only deals in averages and can't speak to things like performance bounds and data latency through a system. To reason about these metrics we turn to network calculus, a theory of systems designed to reason about network bounds [33, 33]. Developed to reason about ATM networks, network calculus borrows concepts from circuit theory and utilizes min-plus algebra to estimate data as it moves through a system. This model retains the same benefits of queuing theory where nodes are separable and can be considered in isolation but also has the benefit of node concatenation, where nodes can be consolidated into a single node for simplicity. Network calculus models can give us absolute bounds on service provided by nodes as well as end-to-end delay on data through the system. The specifics of how the network calculus model are used is expanded upon in Chapter 5.

#### 2.1 Related Work

For the experimental efforts, this work draws from the Data Integration Benchmark Suite (DIBS) [21, 22]. A number of the applications are either members of the benchmark suite, or build on the benchmark suite (e.g., an individual benchmark application that streams data to a downstream data processing application). A number of groups have utilized accelerators for various data integration problems. Fang et al. [39] utilize FPGAs as part of an enterprise ETL operation. Aggarwal [2] explores the use of GPUs for a similar set of tasks. Cabrera and Chamberlain [19, 20] report on the performance of several of the DIBS applications accelerated using FPGAs. Pourhabibi et al. [79] describe Optimus Prime, an ASIC design specifically aimed at data transformations of this type, that is targeted for use as a set of microservices in a distributed environment. Thomas et al. [93] present Fleet, a framework that builds streaming FPGA designs from individual kernels, including data transformation. Fleet aims to automatically parallelise the computation (via replication of the kernels), including the management of data flows to and from external memory units. In addition to data transformation, Fleet is applicable to machine learning applications as well.

Another application we will use is the Basic Local Alignment Search Tool (BLAST) [5, 6]. BLAST is among the most widely used software in bioinformatics. It scans a DNA or protein sequence, the *query*, against a *database* of other sequences to determine which members of the database are most similar to the query under a biologically motivated score equivalent to a weighted string edit distance. In this work, we focus on BLASTN, the variant of BLAST that compares a DNA query to a database of other DNA sequences, such as a genome, a metagenome, or a reference such as GenBank NR.

A representative subset of previous implementations of all or portions of BLAST on accelerators include CAAD BLAST [69], Mercury BLAST [49, 55, 57], RC-BLAST [71], and Tree-BLAST [47] on FPGAs and cuBLASTP [103], GPU-BLAST [98], and Mercury BLAST [67, 77] on GPUs. We utilize the GPU-accelerated Mercury BLAST of Plano and Buhler [77] in our experimental work.

We will apply some of our modeling efforts to an ML application.

Machine learning has long benefited from acceleration. The TensorFlow framework [1] regularly utilizes GPUs, and now is supported by specialized hardware [52]. Zhang et al. [102]

describe a general approach to deploying machine learning applications using convolutional neural networks on FPGAs. Geng et al. [40] use a cluster of FPGAs for ML training, and Li et al. [64] investigate how to partition inference on an FPGA cluster. Sharma et al. [86] start from a domain-specific expression of the ML problem and compile to an FPGA deployment. Liu et al. [66] combine the use of GPUs and FPGAs on a machine learning problem, ultimately concluding that for their problem, GPUs were best suited for the training and FPGAs were best for inference. Shahid and Mushtaq [85] review multiple generations of TPUs on ML problems, comparing them to GPUs and FPGAs, and Reuther et al. [80] survey a wide range of machine learning accelerators.

Our final set of applications include compression and encryption, both of which have a long history of hardware acceleration.

Early work in hardware acceleration of compression algorithms was performed by Huang et al. [48], Rigler et al. [81], and Salama et al. [82]. An LZ4 compression (the one we explore) was reported by Bartík et al. [9]. Early work in FPGA-based acceleration of the AES algorithm includes the efforts of Chodowiec and Gaj [28], Good and Benaissa [42], and Zambreno et al. [101]. Work in this area is sufficiently mature that these functions are now available in libraries provided by the FPGA manufacturers.

The notion of using a high-level language to describe an algorithm to be deployed in hardware has a long history. Streams-C [41] has its origins in streaming computations. ROCCC [97] was an early system that focused on analysis of loops. AutoPilot [104] is the system that eventually evolved into Xilinx's commercial offering. LegUp [23] has a focus on identifying and accelerating a portion of an application that is amenable to FPGA deployment. Cong et al. [31] provided a comprehensive review and vision approximately one decade ago.

There has been significant work recently in the area of optimizing the performance of arbitrary applications implemented on FPGAs using HLS. Examples include the empirically driven approach of Sanaullah et al. [83], constraining the application set to a specific domain (e.g., CNNs) by Sohrabizadeh et al. [89], the use of multi-level intermediate compiler representations by Ye et al. [100], and the exploitation of an affine type system for compile-time analysis [72]. Our work can be considered to be within the scope of this body of work.

A recent review describes applications that exploit more than one accelerator [24] which will be important for the types of tasks we would like to perform utilizing multiple compute

resources on nodes. To this end, we need ways to evaluate such systems and how data flows between them. Queueing theory has long since been used for the design and evaluation for computer systems [3, 53]. The origins of our model, built on queuing theory to measure performance, is described in Chapter 4. It relies on prior work by Dor et al. [34], Padmanabhan et al. [73], Beard and Chamberlain [12], Timcheck and Buhler [94], and Plano and Buhler [78].

Other applications of queueing theory for modeling streaming systems include a queueing network model for a family of cyclic SPMD applications executing on MIMD platforms by Cremonesi and Gennaro [32]. They validate their model on the high-performance applications of a PDE solver and a quantum chemical reaction dynamics code. Another example is a long-lived transaction (LLT) processing system for database management systems (DBMS) modeled by Liang and Tripathi [65]. Here, the performance of the overall transaction processing system being modeled includes the effects of data locking, resource contention, and failure recovery.

Tolosana-Calasanz et al. [95] combine queueing theory models and feedback control mechanisms to provision cloud resources to process data streaming from high data rate sensors. Dor et al. [34] developed an early queueing theory model of BLAST. Finally, Palunčíć et al. [74] survey the development of queueing models for cognitive radio applications.

The above queueing network models make the simplifying assumption that individual queueing station analyses are separable [10]. However, if individual queues fill, in a streaming computation that invokes backpressure on the upstream nodes, which is neglected in a separable analysis. Modeling this form of backpressure has been addressed for M/M/1 queueing systems by Perros and Altiok [76] and extended to Coxian distributions by Krishnamurthy and Chamberlain [56]. However, generalizing to arbitrary arrival and service distributions is a challenge. As a result, we turn to network calculus as an approach to understanding the performance of the system under these conditions.

The application of network calculus is widespread in classical networking systems [7, 8, 60, 84]. These applications, however, are mostly concerned with extensions to other networking models, such as network firewalls [99] and job scheduling [63]. Network calculus also has two sub-branches; one that deals with systems that behave in a stochastic manner, called stochastic network calculus [51], and the other dealing with hard real-time deadlines, known as real-time network calculus [91]. In this particular work we use the standard, deterministic,

network calculus and this is, as far as we know, the first application of these models to streaming computations that specifically target heterogeneous architectures.

## Chapter 3

# Streaming Data Tasks for Heterogeneous Compute

As discussed prior, streaming algorithms are often split up into multiple sections where data is processed and passed onto the next node for completion. Pre-processing algorithms are a wide range of streaming algorithms that are present not only in streaming environments but they are also a component in algorithms that are singleton in nature. These data integration tasks, as mentioned in the introduction, are often not thought about and can become bottlenecks in a full data streaming application when looking at the end to end performance. Unfortunately, it can be hard to reason about improvements for these types of application due to the differences of data structures and implementations. In prior work, effort was expended to categorize and analyse these applications into a set of data integration applications [22] and in this work we specifically want to look at their implementation on heterogeneous platforms, like FPGAs. FPGAs have the wonderful property of being flexible and can be tailor made to suit an an application, but it can often be a bit daunting to program for them as their programming tools can be difficult to utilize. In this work we want to discover what properties and best practices should influence a programmer when implementing data integration applications on an FPGA.

### 3.1 Data Integration Tasks

The set of all data integration tasks have the defining feature of transforming one data record into another data record, but their individual implementations can be quite varied and difficult to reason about. Prior work of defining the space of data integration tasks can be found in the Data Integration Benchmark Suite (DIBS) [21, 22]. Here we spent time to define categories of data integration along with analysing their single threaded performance

and implementation. As shown in Figure 3.1 the applications cross a wide range of target fields and potential data types. At their core most data integration applications take an individual record and transform it into an equivalent record, each record being independent of each other. This type of processing gives rise to a streaming algorithm implementation as each record is processed once, and kept in-order as to preserve the integrity of the data set. These applications were programmed initially in a simple singled threaded manner, but if we want to improve and migrate them to faster, more specialized pieces of hardware it becomes imperative to think about creative ways to move to a parallel implementation.

|                       | Data Integration Tasks                                   |                                                        |                                                           |

|-----------------------|----------------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------|

| Domain                | Parsing/Cleansing                                        | Transformation                                         | Aggregation                                               |

| Computational Biology | Separate bases and meta-data<br>Handle non-A,T,G,C bases | fa→2bit<br>2-bit→fa                                    | Track total size                                          |

| Image Processing      | Parse FITS tags                                          | fits→tiff<br>idx→tiff<br>optdigits→tiff<br>unipen→tiff | Pixel statistics<br>Histogram<br>Taking log of pixels     |

| Enterprise            | Adjust non-ASCII characters                              | ebcdic→txt<br>fix→float                                | Count number of elements                                  |

| Internet of Things    | Tokenize input                                           | tstcsv→csv<br>gotrackcsv→csv<br>plt→csv                | Running total of file size                                |

| Graph Processing      | Parse edge list                                          | edgelist→csr                                           | Get total vertex/edge count<br>Compute vertex edge degree |

Figure 3.1: Data Integration Benchmark Suite application classification [22].

### 3.2 Parallel Implementation

When thinking about accelerating applications in the data integration benchmark suite two things come to mind: what kind of programming model one wants to use and what kind of hardware will be the eventual target. In DIBS most of the statistical analysis showed that a large portion of the programs had low branch entropy and low temporal locality meaning that, as expected, in a majority of the apps the data is transformed with minimal amount of divergence in the processing path and is then stored to the final memory buffer.

When looking at the instruction mix of the x86 implementation, shown in Figure 3.2, we also see that the percentages of instruction mixes can vary from one data integration app to

Figure 3.2: Instruction Mix of DIBS Applications on x86 [22].

another, meaning that one application suited for one hardware target might not be the best fit elsewhere. With these considerations in mind one can either follow a traditional approach of parallelizing via CPU multi-treading or rather pursuing an FPGA implementation due to it's ability to actualize custom architecture that fits an individual data integration application efficiently.

Ideally we want to have an implementation that is easy to move between different platforms, to empirically test and see what platforms are a fit for data integration. The original implementation of DIBS has single threaded implementations of each app coded in the C language compiled for the x86 platform which we use as a starting point for our measurements. While there are many different ways of programming for a multi-threaded implementation ideally we would like to keep as much of the core data integration as similar as possible. When one programs for an FPGA device often the common way is to utilize hardware description languages (HDL) such as VHDL and Verilog to directly program, utilizing modules and IP blocks to actualize hardware. While this is a reasonable approach, most HDLs require a programmer to worry about computation at a cycle by cycle granularity and it can be a burden to layout a system in this way. Both major manufactures of FPGAs (Xilinx and Intel) offer High Level Synthesis (HLS) programming tools that allows a programmer to write code in a higher level language and utilize the tools to parse and create a representation in Verilog which is then used to generate hardware. HLS tools require programming in the C/C++ languages with some restrictions and along with these, C derivatives such as OpenCL can be directly used by the tools and allow a developer to use a model that is inherently parallel.

We took four of these data integration apps and implemented them in OpenCL, a language designed for multi-platform execution targeting CPU, GPU, and FPGA systems. Part of the advantage of taking an OpenCL approach is that we could start with a base computation kernel that looks highly similar to the original C single threaded implementation. From there we took a straightforward implementation, essentially a 1 to 1 copy from the original C code with minor edits for each platform necessary for execution. While it was relatively simple to get a straightforward implementation running well on the CPU it was a bit unclear what would and would not work on FPGA implementation.

### 3.3 Multi-Target OpenCL

In the original OpenCL programming model one writes a "kernel" of computation to be executed on some set of compute units that map to either multi-core CPUs or GPU cores. An individual device has its own set of device memory and execution queue which is managed by a host system, usually the main operating system. When programming a kernel one utilizes OpenCL specific calls to grab a work item identification and articulate how said work is to be done in isolation from other work items. Memory is both allocated and written to the device specific memory via host-side library calls. At the time of enqueuing the kernel execution a number specifying how many work items are to be computed before the kernel is to be considered done and when complete the host is in charge of reading device memory into host side buffers. This programming model for OpenCL is referred to as Multi-Work Item (MWI) and is the typical target for multi-core style systems.

When OpenCL is used in the HLS space the designers of the tools added another programming model called Single-Work Item (SWI) which, along with MWI, allows for styles of execution on the FPGA. A SWI kernel is very similar to the MWI however the difference is instead of using OpenCL API calls to get an ID for work, the amount of work is built into the kernel similar to how one would program a for loop. With this style of execution a kernel is instead queued onto the FPGA with a work size of one, allowing either the amount of work to be hard coded into the kernel or adjustable through kernel arguments. The HLS tools use this type of programming model to implement pipeline parallelism, implementing the hardware needed to perform each instruction and, when the pipeline is full, complete one execution of the main kernel loop within one clock cycle. An illustration of both the MWI

- (a) Multi-work item (MWI) model.

- (b) Single-work item (SWI) model.

Figure 3.3: Illustration of the MWI and SWI OpenCL programming models.

and SWI models is given in Figure 3.3. It may seem on the surface that this would make an even easier porting effort from our single threaded data integration task as one would just have to import the main loop from the code and make the proper API calls for host side execution, however, HLS tools offer a large range of flexibility in optimizations one may add and these are what we want to take into consideration when looking at programmer best practices.

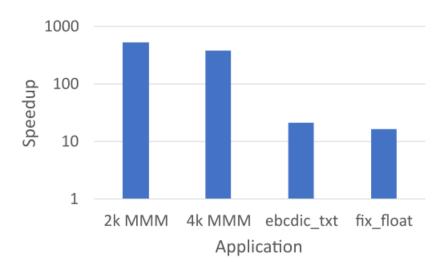

Our experience has not been consistent with the guidance of the FPGA manufacturers with respect to MWI and SWI implementations. We have experience with a number of applications for which the MWI implementation performs better than the SWI implementation. Figure 3.4 shows the speedup of the MWI implementation relative to the SWI implementation for four applications (data from [18, 20, 45]). These four applications can be split into two categories: compute intensive applications in the form of a standard matrix-matrix multiplication and streaming computations drawn from DIBS. To factor out issues with I/O, the input and output data reside in main memory. For the matrix-matrix multiply applications, the MWI implementation outperforms the SWI implementation by more than two orders of magnitude, and the performance of MWI over SWI is more than one order of magnitude for the two applications chosen from DIBS. The measured data throughput for each of the applications is shown in Table 3.1.

Figure 3.4: Speedup of MWI over SWI implementations. Applications are  $2k \times 2k$  and  $4k \times 4k$  matrix-matrix multiply plus data integration applications ebcdic\_txt and fix\_float from DIBS.

Table 3.1: Measured throughputs for MWI and SWI implementations.

| Application  | SWI     | MWI     |

|--------------|---------|---------|

|              | (MiB/s) | (GiB/s) |

| 2k MMM       | 8       | 4.2     |

| 4k  MMM      | 8       | 3.1     |

| $ebcdic_txt$ | 260     | 5.5     |

| $fix_float$  | 400     | 6.5     |

### 3.4 Application Targets and Deployment

To explore implementation details we chose the following benchmark programs from DIBS: fa->2bit, gotrackcsv->csv, fix->float, and idx->tiff. These have the characteristics of being from different fields and a distinct mix of instruction sets and gave a good overview of how these applications would perform on various architectures. Our initial inquiry into these applications was the impact of a sequential dependency in the data transform and how such a dependency would affect performance and how much effort would be required to improve performance. The applications fa->2bit and fix->float have databases that are sequential but their data boundaries are knowable at run-time making an easy transition to a parallel implementation. The application gotrackcsv->csv, has its records separated by a new line character at un-even boundaries requiring an upfront analysis of the database

before the actual data-integration task can begin. The idx->tiff application is similar in that a small amount of metadata processing is required upfront for information on how the images in the database are represented and their size allowing for highly parallel execution after this task. In all instances we consider the total execution time of the data integration task being time spent in the data integration and any metadata processing. In porting these applications over to multi-threaded CPU and FPGA we used an OpenCL implementation with a MWI kernel for the CPU and SWI kernel, at the manufacture's recommendation, for the FPGA.

In this particular experiment we utilized a Xeon E-2256 for CPU deployment and an FPGA from the Hardware Accelerator Research Program (HARP) provided through Intel. The HARP system is a combination of an Arria 10 FPGA and a Xeon Intel CPU connected with a cache coherent bus within the same socket. This specific implementation of a heterogeneous compute FPGA is unique in that the host machine and the compute unit have a unified view of memory meaning that when memory is allocated for the compute device it can accesses it without waiting on a host transfer. It is up to the programmer to setup coherency between the host and device which is handled through shared virtual memory map and unmap commands in the host code. The general program execution first sets up the host for OpenCL execution creating a device handle and command queue for kernel execution, the data integration tasks are then loaded in as kernels. For the CPU target the kernel source code is read in and compiled in real time for execution but for the FPGA target an HLS compiled binary (bitfile) is used for configuration. When a metadata processing step is required its kernel is queued before the the data integration task and the total queue execution time is included as part of the final throughput numbers. Once the data integration task is completed the results are validated and any stats are reported. For all of our data integration application measurements we do not consider the time it takes for data to be read off the disk, but instead only consider data that is active or already in memory, partially due to the fact that such advancements in data retrievement are not the focus of this research and a large number of techniques both in hardware and software exist to try and alleviate this concern [26, 27].

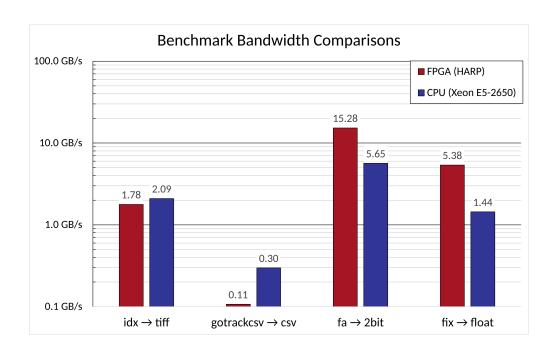

In Figure 3.5 we display the performance numbers for the data integration apps on both target platforms using OpenCL kernel execution. The kernels listed here were ported with minimal effort to both the multi-threaded CPU and FPGA which can be representative of what one might expect base performance to look like on these given systems. First we see the greatest performance with the FPGA in the fa->2bit application, over the

Figure 3.5: Bandwidth comparison numbers for selected DIBS benchmarks running on multicore CPU and HARP FPGA machines.

baseline implementation in the original DIBS this results in a 653× speed up in throughput along with an  $2.7 \times$  speedup over the multi-threaded version. (Note that the original DIBS single-threaded implementations did not include compiler optimizations, which are enabled in these multi-threaded OpenCL implementations.) Similarly, we see a performance boon with fix->float FPGA implementation over the original and multi-threaded versions with a 26× speedup over the single threaded and a 3.7× speedup over multi-threaded. In the idx->tiff application the FPGA is not the top performer compared to the multi-threaded implementation, here we have the metadata processing kernel along with the main processing kernel which points to the notion that cooperative processing might be worth considering here as the transient startup of using an accelerator for one metadata step might not be worth the processing time. Finally looking at the worst performer on the FPGA, gotrackcsv->csv we have a marginal increase of throughput over the base single-threaded implementation of roughly 10 MB/s. There are a multitude of reasons for why this app has poor performance. Mostly, the performance can be attributed to the control flow present in this particular app and the amount of times it accesses global memory. The app's processing path reads in characters one at a time looking for boundaries noted by the comma character and once a certain amount is seen a branching path is enabled to remove data from the structure. This causes a very irregular execution pattern for this app and because each line has a variable amount of characters in each line it becomes difficult to determine ahead of time where these boundaries are. Furthermore, a metadata step is required up front to determine where line breaks exist in the database adding more processing time not suited for FPGA computation.

### 3.5 Improving Kernel Implementations

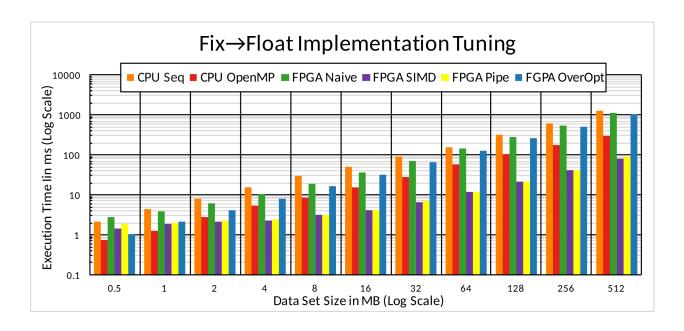

Building upon naive approaches we wanted to look at HLS features that one could add to a kernel in order to improve performance across all apps. For this approach we attempted to compare both FPGA and CPU performance on one app with a plethora of varying setups, including an OpenMP CPU Implementation, and were performed on the HARP system. In FPGA HLS tools as mentioned prior there are two coding styles for OpenCL kernels: MWI and SWI; with these there are also extra additional options and flags that can be added to the kernel that can affect performance. As it can take hours to compile kernels in multiple configurations we settled on 4 different configurations to observe: A naive SWI kernel with no pipeline flags enabled, SWI kernel with a flag to pipeline as aggressively as possible (our kernel from above), A MWI kernel with the largest work-group size as possible (64 for our tools), and what we call an "over-optimized" kernel which is a a MWI kernel with the largest work-group size as possible, 2 total compute units, and a SIMD work item count of 16. The OverOpt kernel is meant to represent a scenario where a potentially confused programmer might try to do everything under the sun to try and improve a FPGA kernel without giving too much consideration to the hardware that they are targeting. While we expected to see somewhat poor performance we were curious which choice in kernel style would compare to multi-threaded CPU execution.

Figure 3.6 shows the execution time of the fix->float application on a log scale with respect to database size also in a log scale. Here on this graph a lower bar indicates better performance. From the outset for a considerably small database of 512Kb we observe the the OverOpt Kernel actually performs quite well and is only beaten out by the OpenMP CPU implementation, however, as the data set size increases this observation will not hold. We observe a breaking point between the multi-threaded CPU and the FPGA MWI and SWI implementations, but along with this we see the OverOpt kernel begins to run away and only outperform a naive implementation and a single threaded implementation. Interestingly, this

Figure 3.6: Data size vs. execution time on HARP for versions of the fix->float kernel.

trend continues as we increase the database size and in fact the performance gap between the kernels with less attributes for the HLS engine and the kernel made in an attempt to improve performance only gets larger. Furthermore, a closer inspection between the MWI model and the SWI model shows that, for this one application, a MWI model actually has a slightly better performance than the SWI contrary to what is suggested by the manufacturer. While this is only one application this test is run on it does paint an interesting picture of what general programming advice we would like to give.

#### 3.6 Programming Advice

Currently through our research we have found a few guidelines that we believe can be applicable across multiple data integration applications implemented on FPGAs. With our examples on the HARP system, three main points come to mind: data transforms with data dependencies, divergent data transforms, data transforms with metadata processing. Data transforms that have both data dependencies and divergent execution paths cause the same issue on FPGA implementation: an inability to pipeline efficiently for unrolled loops. When the HLS tools analyze kernel loops it does so in an attempt to reduce the amount of cycles required for each instruction. When divergence is introduced, such as an if else statement,

the compiler will generate an execution path that will take the time to execute the largest path. Data dependencies, similarly, will cause the tools to create loops that have long cycles between each loop iteration, causing execution time to increase significantly. Metadata processing is a different problem in that this is a bit of execution that needs to be done upfront and separate from the main kernel loop. Processing situations where an entire dataset may need to be parsed for metadata can lead to divergent processing if the kernel is looking and marking the location of certain characters. Other metadata situations may only require a small amount of data to process. In our second experiment we can deduce that the transient startup costs of FPGA execution may not outweigh the benefits of specialized execution as a single threaded CPU implementation can beat out a FPGA kernel. While the data integration task measured in the second experiment did not deal with a meta processing task the small database size could be indicative of smaller processing tasks.

Looking further beyond the database size implications in the second task we note the runaway performance as mentioned above. A large portion of the improvements chosen here were meant to be indicative of a programmer trying to squeeze performance out of a HLS kernel. Often when implemented at first blush a programmer will often see terrible performance when it comes to FPGAs. As such a developer might see a large portion of the FPGA be unused and as such try to do reasonable things such as increasing the number of compute units or increasing the number of SIMD work items and the issue arises when the generated hardware does not match what is required to perform the computation efficiently. In this case the extra compute units create more contention for the shared memory bus which is not ideal for our data integration applications as our applications are mostly made of memory movement instructions demonstrated by the instruction count mix shown in Figure 3.2. This is of course exacerbated with the addition of more SIMD work items increasing the memory requests in parallel. Such advice could be applied to data integration tasks on FPGAs that take this form of regular isolated tasks.

The Xilinx Vitis toolchain has attempted to improve SWI implementations with a programming strategy available for both OpenCL and C HLS kernels known as *dataflow optimization*. In the documentation, dataflow optimization is described as a way to implement "task-level pipelining," which allows for code blocks contained in functions to be scheduled in a way to achieve pipeline parallelism, similar to the approach that loop unrolling does within a loop. As shown in Figure 3.7, the idea is to create a collection of tasks or functions that would normally run in sequence and allow the compiler, with the help of **#pragma** directives, to

create hardware that allows for execution of downstream tasks to start before their preceding task has completed. This is achieved through the use of first-in-first-out (FIFO) buffers to pass data elements from one code block to the next. These code blocks could be some type of read from global memory, general compute functionality, then a write back to global memory, which allows the hardware to take advantage of blocked reads and writes. Ideally, this type of coding style, as the name suggests, can work well for data streaming applications such as the previously mentioned data integration applications.

Figure 3.7: Illustration of dataflow execution with 3 tasks. The top diagram illustrates a sequential execution timeline, while the bottom diagram illustrates a pipelined execution timeline.

Using this technique, we have seen success deploying a data integration application as a dataflow kernel, with performance better than the MWI and even the initial SWI implementation. However, it is important to note that in other data integration applications we see that this style of kernel does not perform quite as well as expected. In an experiment implementing a handwriting database from an ASCII picture representation to a bit array representation (the optidigits application from DIBS) we find that the best performance is with the original SWI programming model with a throughput of 221 MiB/s. Believing that the dataflow approach would result in better performance, we made a pair of attempts using it. With our first attempt at the dataflow model we observed a slight reduction in throughput to 218 MiB/s. While a reduction of roughly 3% in throughput is arguably negligible, it still gives pause to what implementation strategies developers should choose.

#### 3.7 Conclusion

Streaming data tasks, while being sometimes difficult to implement, can see performance improvements from heterogeneous architecture. The difficulty stems from a need to fully understand the algorithm before deployment but this could be said of almost any performance engineer for any type of algorithm. When it comes to data integration often time emphasis is put on data movement which can often be a pain point for these types of applications. Here we explored implementing data integration tasks on multiple types of hardware utilizing OpenCL and focusing in on FPGAs as an execution platform. While FPGAs show promise in this field it is not without its own caveats and here we have pointed out some of the difficulties one may have when implementing data integration tasks. We have explored two types of programming styles: MWI which takes a thread-based work item approach and SWI which is a deeply pipe-lined approach utilizing for loops. When implementing effective programming strategies it is critical to not only have an understanding of how the algorithm handles memory access, where that memory access is originating from, and how memory hierarchies interact with eachother. With these interactions in mind a developer may spend some time implementing one piece of a data streaming algorithm without focusing on the higher level interactions of other nodes in the process. Stepping back and looking at the larger picture can be somewhat difficult, however, we address these concerns with mathematical models that help a developer reason about performance beyond individual node implementation.

### Chapter 4

# Queueing Models for Streaming Data Computation

#### 4.1 Introduction

While we have spent some time describing the characteristics of data streaming applications in the form of data integration, however, it is important to remember that they do not exist on their own. When including data integration as a step in an overall streaming application the system inherently becomes more complex, and the use of an effective performance model can be used as a concrete way to reason about both the application and its deployment. On top of that there may be scenarios where different instances of computational accelerators may be used to run different portions of the overall algorithm. These accelerators may exist on the same platform or on entirely separate nodes. There can be a large number of potential deployment options and configuration settings that can impact performance, and it can be difficult to pinpoint where time and resources need to be spent and what to budget.

We propose an empirically guided mathematical model to help guide performance choices in the streaming algorithms that seeks to find a throughput roofline for a given application and takes into account data compression/expansion with data integration applications. It also includes cost information (if available), so that the deployment choices can be based on cost-benefit analyses, not just throughput performance.

## 4.2 Applications

The two applications used to illustrate the models in this chapter are BLAST and an ML handwriting recognition application. We describe each in turn.

#### 4.2.1 BLAST

The stages of our BLASTN implementation mirror the stages of the NCBI BLASTN computation pipeline, shown in Figure 4.1, and is built using the Mercator framework on a GPU [30]. The DNA database to be searched, represented in FASTA format, is first converted to two bits per DNA base. This is a pre-processing step, fa\_2bit, from DIBS that is implemented on an FPGA [37]. In the next computational stage, seed match, each bytealigned 8-mer (8-base word) of the database is checked to see whether it appears in a hash table (stored in GPU DRAM) constructed from all 8-mers of the query sequence. If the 8-mer at database position p does appear in the table, a third stage, seed enumeration, accesses the table to enumerate all positions q at which it appears, generating one or more 8mer matches (p,q). These matches are passed to the fourth stage, small extension, which attempts to extend each match to the left and right by up to 3 bases. If a match (p,q) can be extended to a total length of at least 11, it is passed on to the final stage, ungapped extension, which extends the match to the left and right, this time allowing scoring of both matches and mismatches. Our implementation limits ungapped extension to at most a fixedsize window (currently 128 bases) centered on the initial seed match. Only seed matches whose highest-scoring ungapped extension score above a specified threshold are returned for further processing. Our implementation does not presently perform gapped extension [6], but for BLASTN, that stage takes negligible time compared to the rest of the pipeline [55] and would be implemented on the host processor.

Figure 4.1: BLAST application.

Most stages of BLASTN act as filters over either database positions (seed matching) or matches (small and ungapped extension). Their task is to eliminate inputs that should not proceed to the next stage. Seed matching in particular is a highly effective filter, eliminating the vast majority of input 8-mers, for query lengths much less than  $2^{16}$  bases. Seed enumeration, in contrast, may produce multiple matches per input position if the same 8-mer occurs at several places in the query. Except for highly repetitive query sequences, this stage produces on average 1-2 matches per input position.

All stages of BLASTN produce a variable number of outputs per input, and most produce zero outputs for the majority of their inputs. On a SIMD processor such as a GPU, executing all stages of BLASTN independently in each thread will result in many threads discarding their inputs and becoming idle early in the computation, resulting in many wasted cycles. The Mercator system therefore inserts queues between each stage to collect and redistribute work among threads before executing the next stage. These queues have limited size, so each stage may need to be executed multiple times; scheduling execution of stages is performed so as to maximize GPU thread occupancy and minimize overhead [77].

#### 4.2.2 ML